Altera RapidIO MegaCore Function User Manual

Page 123

Chapter 5: Signals

5–9

Physical Layer Signals

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

In addition to customization of the transceiver through the parameter editor (in

variations that target a device for which the transceivers are configured with the

ALTGX megafunction, and not with the Transceiver PHY IP core), you can use the

transceiver reconfiguration block to dynamically modify the parameter interface. The

dynamic reconfiguration block lets you reconfigure the following PMA settings:

■

Pre-emphasis

■

Equalization

■

Offset cancellation

■

V

OD

on a per channel basis

The dynamic reconfiguration block is required for many device families, including

Arria V, Cyclone V, and Stratix V devices. Refer to

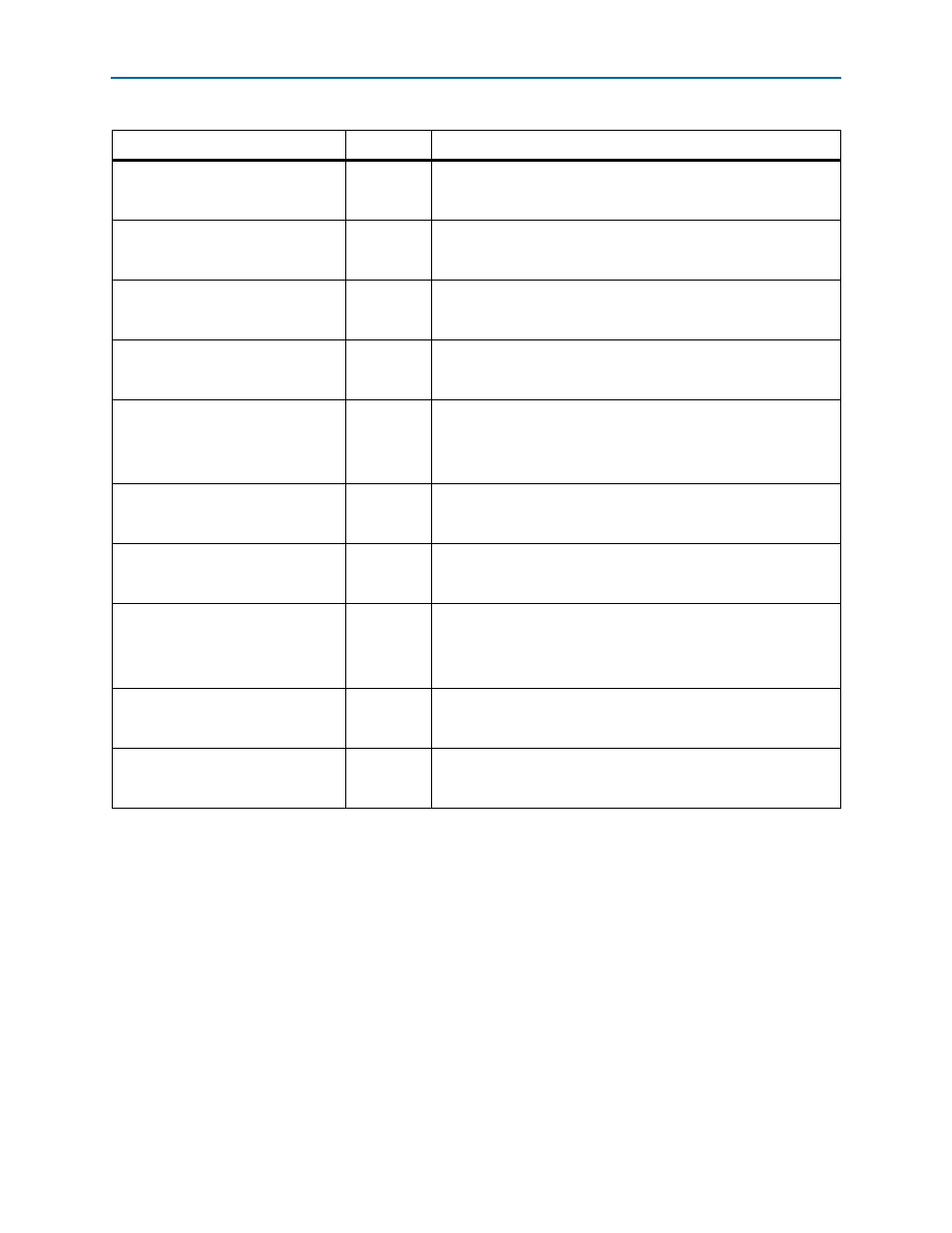

reconfig_writedata_ch2[31:0]

Input

Arria 10 dynamic reconfiguration slave write data bus for the

transceiver channel configured for RapidIO lane 2. This signal is

available only in 4x variations.

reconfig_readdata_ch2[31:0]

Output

Arria 10 dynamic reconfiguration slave read data bus for the

transceiver channel configured for RapidIO lane 2. This signal is

available only in 4x variations.

reconfig_clk_ch3

Input

Arria 10 dynamic reconfiguration interface clock for the transceiver

channel configured for RapidIO lane 3. This signal is available only in

4x variations.

reconfig_reset_ch3

Input

Arria 10 dynamic reconfiguration interface reset for the transceiver

channel configured for RapidIO lane 3. This signal is available only in

4x variations.

reconfig_waitrequest_ch3

Output

Arria 10 dynamic reconfiguration slave wait request for the

transceiver channel configured for RapidIO lane 3. The RapidIO IP

core uses this signal to stall the requestor on the interconnect.

This signal is available only in 4x variations.

reconfig_read_ch3

Input

Arria 10 dynamic reconfiguration slave read request for the

transceiver channel configured for RapidIO lane 3. This signal is

available only in 4x variations.

reconfig_write_ch3

Input

Arria 10 dynamic reconfiguration slave write request for the

transceiver channel configured for RapidIO lane 3. This signal is

available only in 4x variations.

reconfig_address_ch3[9:0]

Input

Arria 10 dynamic reconfiguration slave address bus for the

transceiver channel configured for RapidIO lane 3. The address is a

word address, not a byte address.

This signal is available only in 4x variations.

reconfig_writedata_ch3[31:0]

Input

Arria 10 dynamic reconfiguration slave write data bus for the

transceiver channel configured for RapidIO lane 3. This signal is

available only in 4x variations.

reconfig_readdata_ch3[31:0]

Output

Arria 10 dynamic reconfiguration slave read data bus for the

transceiver channel configured for RapidIO lane 3. This signal is

available only in 4x variations.

Table 5–9. Arria 10 Transceiver Dynamic Reconfiguration Avalon-MM Interface Signals (Part 3 of 3)

Signal

Direction

Description