Transmit maintenance registers, Transmit port-write registers, Table 6–30 – Altera RapidIO MegaCore Function User Manual

Page 150: Table 6–31, Table 6–32

6–18

Chapter 6: Software Interface

Transport and Logical Layer Registers

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

Transmit Maintenance Registers

through

describe the transmitter maintenance registers. When

transmitting a MAINTENANCE packet, an address translation process occurs, using a

base, mask, offset, and control register. As many as sixteen groups of four registers

can exist. The 16 register address offsets are shown in the table titles. For more details

on how to use these windows, refer to

“Maintenance Slave Processor” on page 4–28

.

Transmit Port-Write Registers

through

describe the transmit port-write registers.

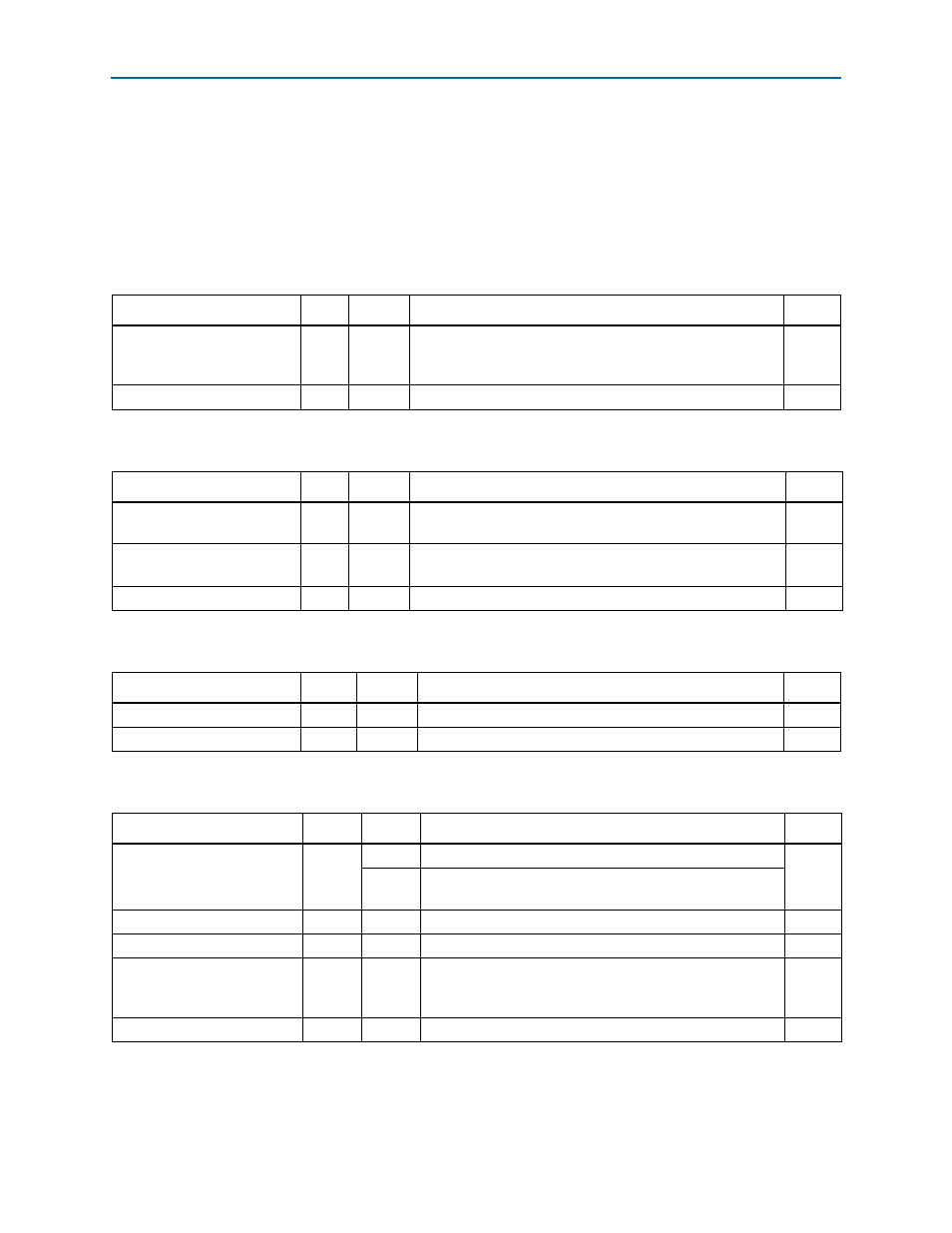

Table 6–29. Tx Maintenance Mapping Window n Base—Offset: 0x10100, 0x10110, 0x10120, 0x10130, 0x10140,

0x10150, 0x10160, 0x10170, 0x10180, 0x10190, 0x101A0, 0x101B0, 0x101C0, 0x101D0, 0x101E0, 0x101F0

Field

Bits

Access

Function

Default

BASE

[31:3] RW

Start of the Avalon-MM address window to be mapped. The

three least significant bits of the 32-bit base are assumed to be

zero.

29'h0

RSRV

[2:0]

RO

Reserved

3'h0

Table 6–30. Tx Maintenance Mapping Window n Mask—Offset: 0x10104, 0x10114, 0x10124, 0x10134, 0x10144,

0x10154, 0x10164, 0x10174, 0x10184, 0x10194, 0x101A4, 0x101B4, 0x101C4, 0x101D4, 0x101E4, 0x101F4

Field

Bits

Access

Function

Default

MASK

[31:3] RW

Mask for the address mapping window. The three least

significant bits of the 32-bit mask are assumed to be zero.

29'h0

WEN

[2]

RW

Window enable. Set to one to enable the corresponding

window.

1'b0

RSRV

[1:0]

RO

Reserved

2'h0

Table 6–31. Tx Maintenance Mapping Window n Offset—Offset: 0x10108, 0x10118, 0x10128, 0x10138, 0x10148,

0x10158, 0x10168, 0x10178, 0x10188, 0x10198, 0x101A8, 0x101B8, 0x101C8, '0x101D8, 0x101E8, 0x101F8

Field

Bits

Access

Function

Default

RSRV

[31:24] RO

Reserved

8'h0

OFFSET

[23:0]

RW

Window offset

24'h0

Table 6–32. Tx Maintenance Mapping Window n Control—Offset: 0x1010C, 0x1011C, 0x1012C, 0x1013C, 0x1014C,

0x1015C, 0x1016C, 0x1017C, 0x1018C, 0x1019C, 0x101AC, 0x101BC, 0x101CC, 0x101DC, 0x101EC, 0x101FC

Field

Bits

Access

Function

Default

LARGE_DESTINATION_ID

(MSB)

[31:24]

RO

Reserved if the system does not support 16-bit device ID.

8'h0

RW

MSB of the Destination ID if the system supports 16-bit

device ID.

DESTINATION_ID

[23:16]

RW

Destination ID

8'h0

HOP_COUNT

[15:8]

RW

Hop count

8'hFF

PRIORITY

[7:6]

RW

Packet priority.

2’b11 is not a valid value for the PRIORITY field. Any attempt

to write 2’b11 to this field is overwritten with 2’b10.

2'b00

RSRV

[5:0]

RO

Reserved

6'h0