Port-write transactions, Port-write transactions –10 – Altera RapidIO MegaCore Function User Manual

Page 172

7–10

Chapter 7: Testbenches

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

In the first part of this test, the bfm_drbell_master sends a Doorbell message one clock

cycle after the bfm_io_write_master sends a write request. Write requests are sent and

checked according to the test sequence described in

, and Doorbell messages are sent and checked according to the test sequence

described in

“Doorbell Transactions” on page 7–8

. The additional hardware shown in

is used to compare the transaction order before and after transmission on

the RapidIO link. Each queue has 40 bits of FIFO data. In each queue, the current

entry is set to 0 for a write request and to 1 for a Doorbell message. The comparator

compares bit by bit, checking for an exact match.

In the second part of this test, the DUT asserts an invalid byteenable value on the I/O

slave port for a single NWRITE_R transaction, and then transmits 32 NWRITE_R

transactions with a target address set out of bounds. After the bfm_io_write_master

initiates the sequence of NWRITE_R transactions, the bfm_drbell_master generates

transactions as in

“Doorbell Transactions” on page 7–8

. Each Doorbell transaction is

sent to the DUT immediately following a different NWRITE_R transaction. In

addition to checking for data integrity and for transaction order preservation despite

the tracking complication of cancelled transactions, the testbench checks that the I/O

Slave Interrupt

register reflects each cancelled transaction correctly.

Port-Write Transactions

To test port-writes, the test performs some basic configuration of the port-write

registers in the DUT and the sister_rio module. It then programs the DUT to transmit

port-write request packets to the sister_rio module. The port-writes are received by

the sister_rio module and retrieved by the test program.

The configuration enables the Rx packet stored interrupt in the sister_rio module.

With the interrupt enabled, the sister_rio module asserts the sister_sys_mnt_s_irq

signal, which indicates that an interrupt is set in either the Maintenance Interrupt

register or the Input/Output Slave Interrupt register. Because this part of the

testbench is testing port writes, the assertion of sister_sys_mnt_s_irq means that a

Port-Write transaction has been received and that the payload can be retrieved. To

enable the interrupt, call the task rw_addr_data defined in the sister_bfm_cnt_master

module.

A write operation is performed by the task with the address 0x10084 and data 0x10

passed as parameters. In addition, the sister_rio module must be enabled to receive

Port-Write transactions from the DUT. The task is called with the address 0x10250 and

data 0x1.

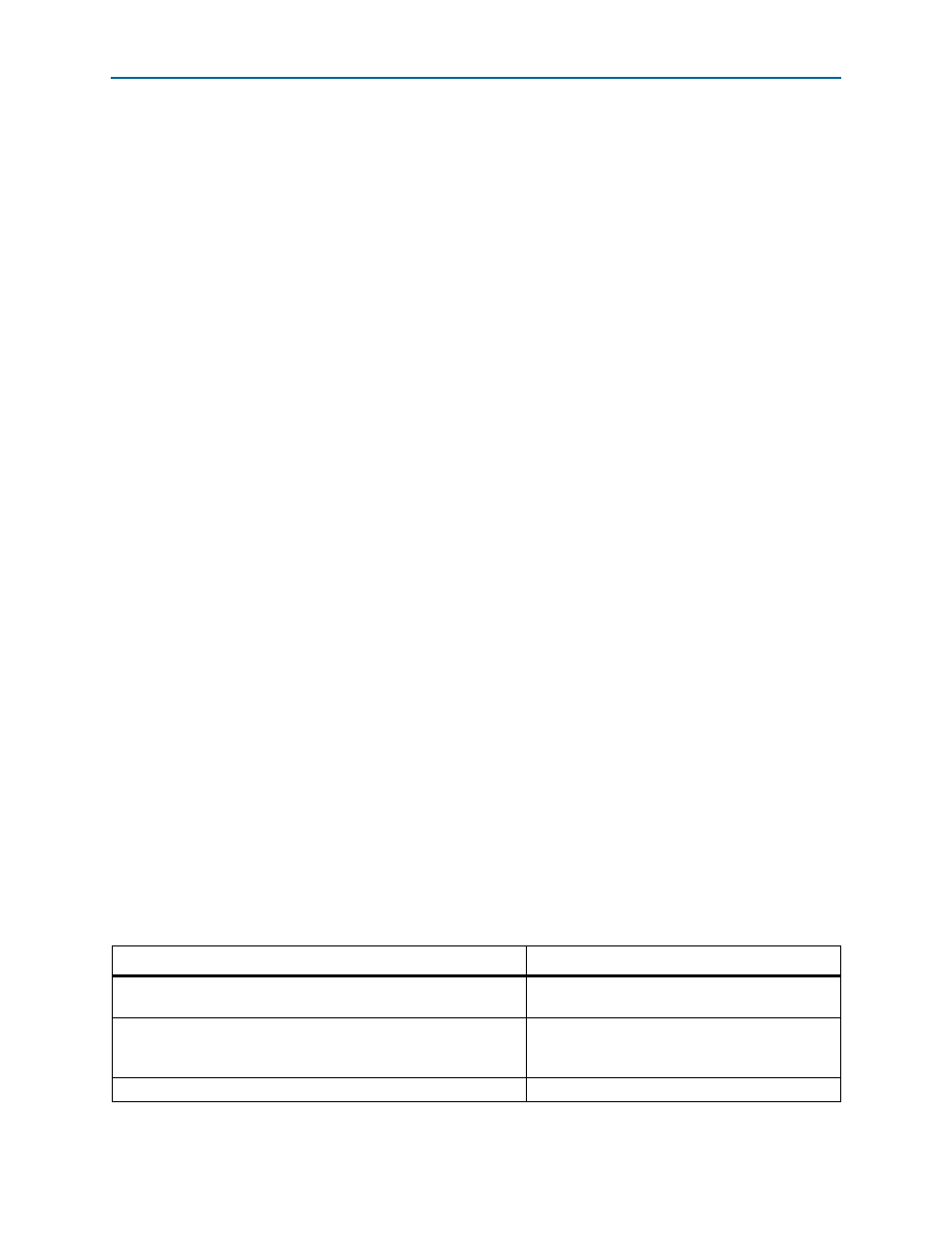

After the configuration is complete, the test performs the operations listed in

.

Table 7–5. Port-Write Test

Operation

Action

Places data into the TX_PORT_WRITE_BUFFER

Write incrementing payload to registers at

addresses 0x10210 to 0x1024C

Indicates to the DUT that Port-Write data is ready

Write DESTINATION_ID = 0x55 or 0x5555,

depending on the device ID width setting, and

PACKET_READY

= 0x1 to 0x10200

Waits for the sister_rio module to receive the port-write

Monitor sister_sys_mnt_s_irq