Physical layer registers, Physical layer registers –4 – Altera RapidIO MegaCore Function User Manual

Page 136

6–4

Chapter 6: Software Interface

Physical Layer Registers

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

Physical Layer Registers

shows the memory map for the RapidIO Physical layer.

through

describe the registers for the Physical layer of the RapidIO IP core. The

offset values are defined by the RapidIO standard.

0x1030C

Reserved

—

0x10310–0x103FC

I/O

Master Windows 1–15

Input/Output Master Logical layer

0x10400

I/O

Slave Window 0 Base

Input/Output Slave Logical layer

0x10404

I/O

Slave Window 0 Mask

Input/Output Slave Logical layer

0x10408

I/O

Slave Window 0 Offset

Input/Output Slave Logical layer

0x1040C

I/O

Slave Window 0 Control

Input/Output Slave Logical layer

0x10410-0x104FC

I/O

Slave Windows 1–15

Input/Output Slave Logical layer

0x10500

I/O

Slave Interrupt

Input/Output Slave Logical layer

0x10504

I/O

Slave Interrupt Enable

Input/Output Slave Logical layer

0x10508

I/O Slave Pending NWRITE_R

Transactions

Input/Output Slave Logical Layer

0x1050C

I/O Slave Avalon-MM Write

Transactions

Input/Output Slave Logical layer and Doorbell module

0x10510

I/O Slave RapidIO Write

Requests

Input/Output Slave Logical layer and Doorbell module

0x10514–0x105FC

Reserved

—

0x10600

Rx Transport Control

Transport layer

0x10604–0x107FC

Reserved

—

0x10800

Logical/Transport

Layer Error

Detect

Logical/Transport layer

0x10804

Logical/Transport

Layer Error

Enable

Logical/Transport layer

0x10808

Logical/Transport

Layer Address Logical/Transport layer

0x1080C

Logical/Transport

Layer Device

ID

Capture

Logical/Transport layer

0x10810

Logical/Transport

Layer Control

Capture

Logical/Transport layer

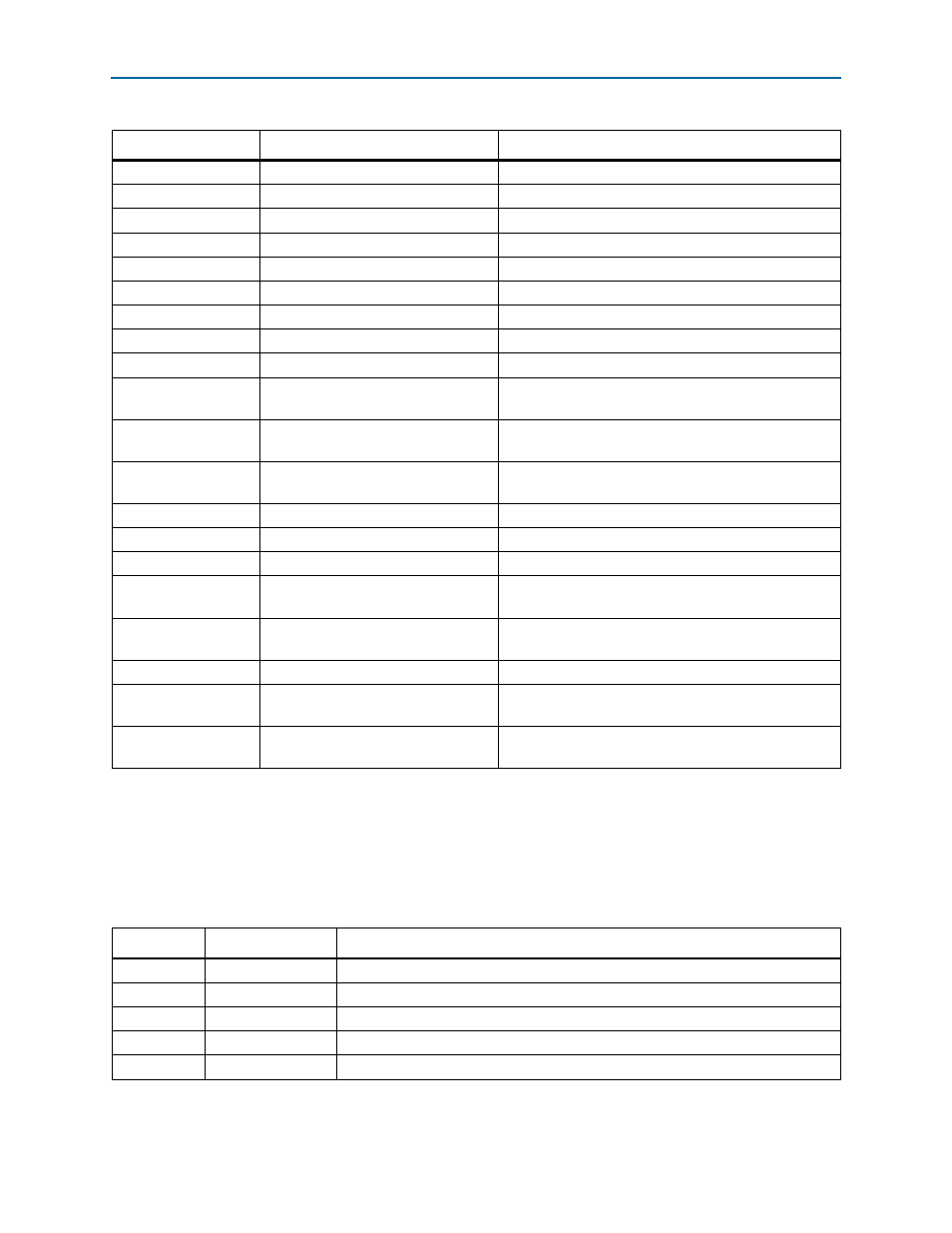

Table 6–2. Memory Map (Part 3 of 3)

Address

Name

Used by

Table 6–3. Physical Layer Register Map (Part 1 of 2)

Address

Name

Description

0x100

PHEAD0

LP-Serial Register Block Header

0x104

PHEAD1

Reserved register

0x120

PLTCTRL

Port Link Time-out Control CSR

0x124

PRTCTRL

Port Response Time-out Control CSR

0x13C

PGCTRL

Port General Control CSR