Integrating your ip core in your design, Calibration clock, Dynamic transceiver reconfiguration controller – Altera RapidIO MegaCore Function User Manual

Page 27: Integrating your ip core in your design –5

Chapter 2: Getting Started

2–5

Integrating Your IP Core in Your Design

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

1. For non-Arria 10 variations only, change directory to

<your_ip>/simulation/submodules.

2. For non-Arria 10 variations only, type the following command to update the

simulation scripts in the simulator-specific directories:

do srio_simulator.tcl

r

3. Change directory to the location of the testbench script,

<your_ip>/simulation/synopsys/vcs.

4. Type the following command to set up the required libraries, compile the

generated IP functional simulation model, and exercise the simulation model with

the provided testbench:

sh vcs_setup.sh TOP_LEVEL_NAME="tb"

./simv

Integrating Your IP Core in Your Design

When you integrate your IP core instance in your design, you must pay attention to

some additional requirements. If you generate your IP core from the Qsys IP catalog

and build your design in Qsys, you can perform these steps in Qsys. If you generate

your IP core directly from the Quartus II IP catalog, you must implement these steps

manually in your design.

Calibration Clock

For Arria II GX, Arria II GZ, Cyclone IV GX, and Stratix IV GX designs, ensure that

you connect the calibration clock (cal_blk_clk) to a clock signal with the appropriate

frequency range of 10 to 125 MHz. The cal_blk_clk ports on other components that

use transceivers must be connected to the same clock signal.

Dynamic Transceiver Reconfiguration Controller

RapidIO IP core variations that target an Aria 10 device include a reconfiguration

controller block and do not require an external reconfiguration controller. All other

RapidIO IP core variations require an external reconfiguration controller to function

correctly in hardware.

For Arria II GX, Arria II GZ, Cyclone IV GX, and Stratix IV GX designs with

high-speed transceivers, you must add a dynamic reconfiguration block

(altgx_reconfig) to your design. You must connect it as specified in

e

r the

This block supports offset cancellation. The design compiles without the

altgx_reconfig

block, but it cannot function correctly in hardware.

f

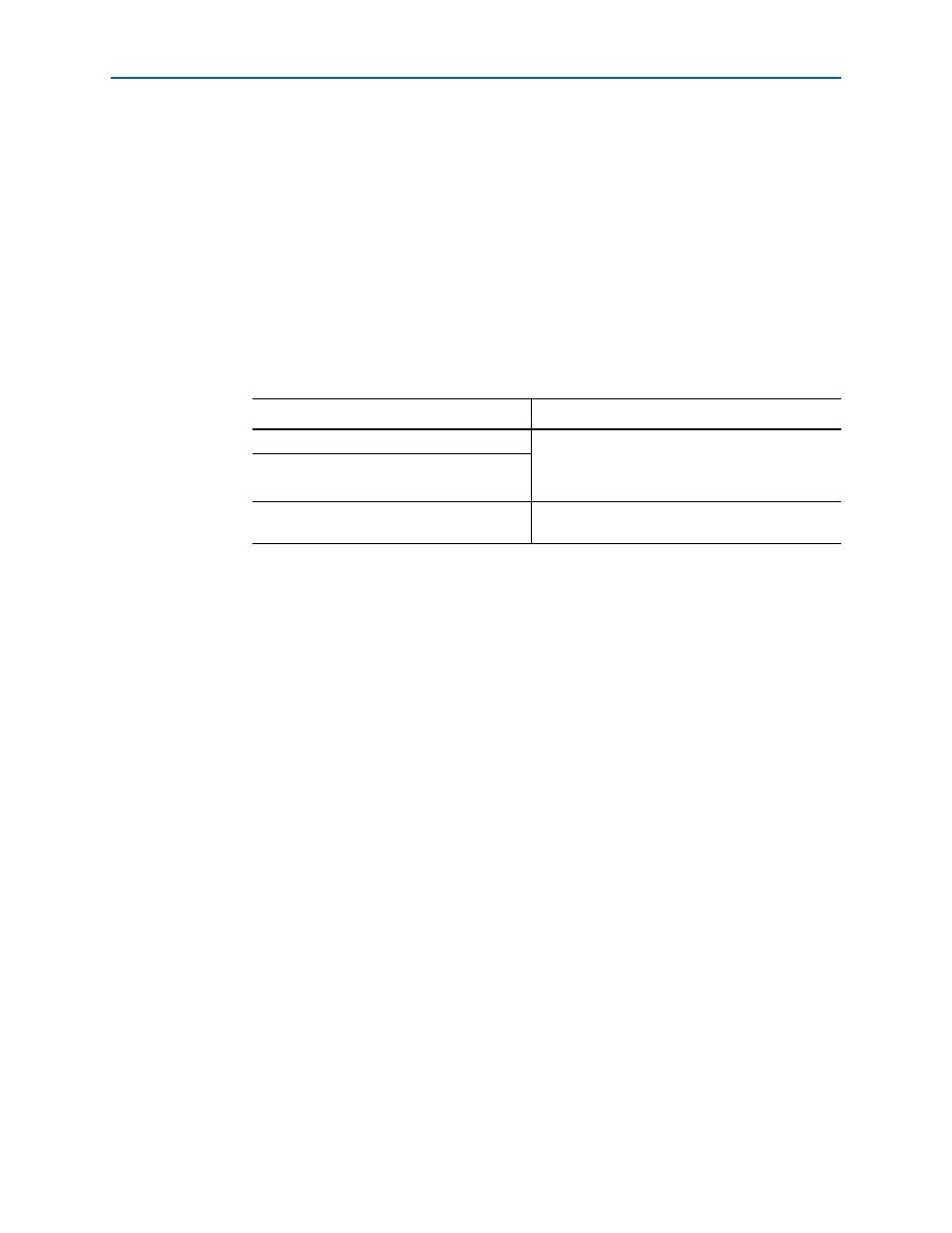

For Information About

Refer To

Quartus II software

See the Quartus II Help topics:

“About the Quartus II Software”

“About the IP Catalog”

IP Catalog

Altera simulation models

chapter in volume 3 of

the Quartus II Handbook