Altera RapidIO MegaCore Function User Manual

Page 121

Chapter 5: Signals

5–7

Physical Layer Signals

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

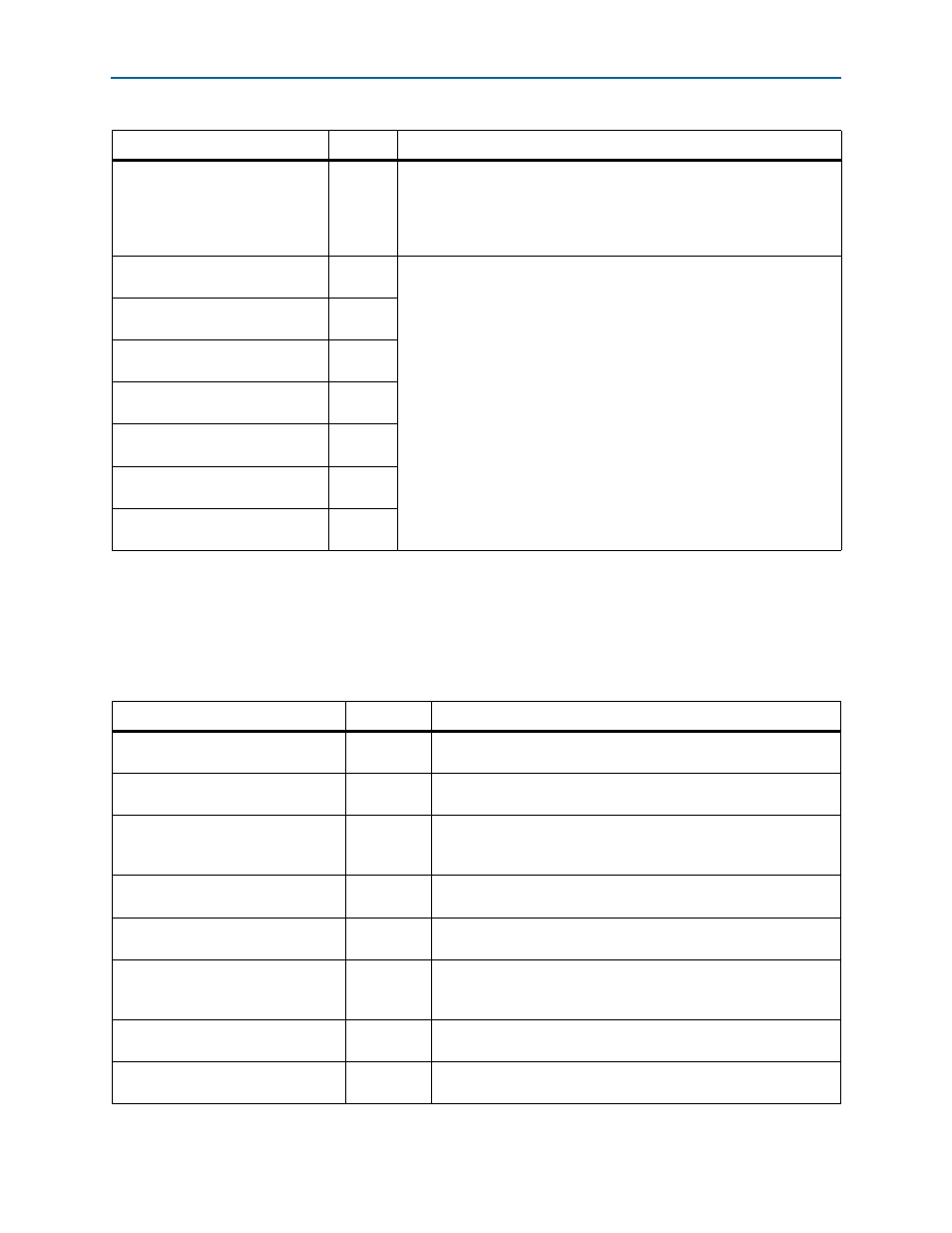

tx_bonding_clocks_ch3[5:0]

Input

Transceiver channel TX input clocks for RapidIO lane 3. This signal is

available only in Arria 10 4x variations. Each transceiver channel that

corresponds to a RapidIO lane has six input clock bits. The bits are

expected to be driven from a TX PLL. Refer to

tx_analogreset

[

Input

These signals are documented in the

.

You must connect these signals to an Altera Transceiver PHY Reset

Controller IP core, which implements the appropriate reset sequence for

the device. Connect each signal to the corresponding signal in the

Transceiver PHY Reset Controller IP core.

These signals are available only in Arria 10 IP core variations.

rx_analogreset

[

Input

tx_digitalreset

[

Input

rx_digitalreset

[

Input

rx_is_lockedtodata

[

Output

tx_cal_busy

[

Output

rx_cal_busy

[

Output

Notes to

Table 5–8

:

(1) You connect this clock inside the Qsys tool. If you connect it to an external clock, a port with the name of that external clock is added to your

Qsys system and this clock is connected to it.

(2) Refer to

“Instantiating Multiple RapidIO IP Cores” on page 2–10

for information about how to successfully combine multiple high-speed

transceiver channels—whether in two RapidIO IP core instances or in a RapidIO IP core and in another component—in the same transceiver

block.

Table 5–8. Transceiver Signals (Part 4 of 4)

Signal Direction

Description

Table 5–9. Arria 10 Transceiver Dynamic Reconfiguration Avalon-MM Interface Signals (Part 1 of 3)

Signal

Direction

Description

reconfig_clk_ch0

Input

Arria 10 dynamic reconfiguration interface clock for the transceiver

channel configured for RapidIO lane 0.

reconfig_reset_ch0

Input

Arria 10 dynamic reconfiguration interface reset for the transceiver

channel configured for RapidIO lane 0.

reconfig_waitrequest_ch0

Output

Arria 10 dynamic reconfiguration slave wait request for the

transceiver channel configured for RapidIO lane 0. The RapidIO IP

core uses this signal to stall the requestor on the interconnect.

reconfig_read_ch0

Input

Arria 10 dynamic reconfiguration slave read request for the

transceiver channel configured for RapidIO lane 0.

reconfig_write_ch0

Input

Arria 10 dynamic reconfiguration slave write request for the

transceiver channel configured for RapidIO lane 0.

reconfig_address_ch0[9:0]

Input

Arria 10 dynamic reconfiguration slave address bus for the

transceiver channel configured for RapidIO lane 0. The address is a

word address, not a byte address.

reconfig_writedata_ch0[31:0]

Input

Arria 10 dynamic reconfiguration slave write data bus for the

transceiver channel configured for RapidIO lane 0.

reconfig_readdata_ch0[31:0]

Output

Arria 10 dynamic reconfiguration slave read data bus for the

transceiver channel configured for RapidIO lane 0.