Input/output slave mapping registers, Input/output slave mapping registers –21, Table 6–41 – Altera RapidIO MegaCore Function User Manual

Page 153

Chapter 6: Software Interface

6–21

Transport and Logical Layer Registers

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

Input/Output Slave Mapping Registers

through

describe the Input/Output slave registers. The

registers define windows in the Avalon-MM address space that are used to determine

the outgoing request packet’s ftype, DESTINATION_ID, priority, and address fields.

There are up to 16 register sets, one for each possible address mapping window. The

16 possible register address offsets are shown in the table titles.

Refer to

“Input/Output Avalon-MM Slave Address Mapping Windows” on

for a description of how to use these registers.

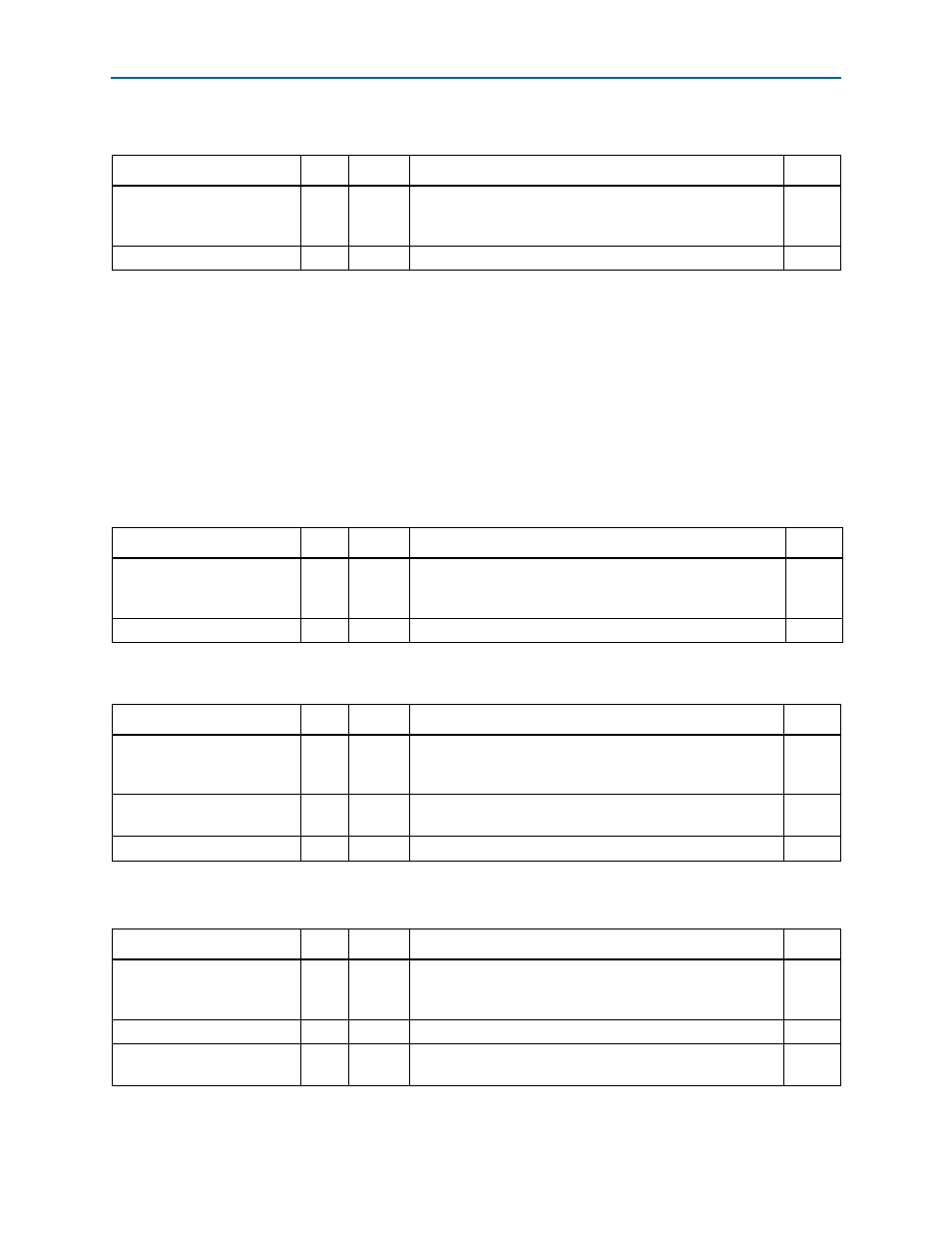

Table 6–41. Input/Output Master Mapping Window n Offset—Offset: 0x10308, 0x10318, 0x10328, 0x10338, 0x10348,

0x10358, 0x10368, 0x10378, 0x10388, 0x10398, 0x103A8, 0x103B8, 0x103C8, 0x103D8, 0x103E8, 0x103F8

Field

Bits

Access

Function

Default

OFFSET

[31:3] RW

Starting offset into the Avalon-MM address space. The three

least significant bits of the 32-bit offset are assumed to be

zero.

29'h0

RSRV

[2:0]

RO

Reserved

3'h0

Table 6–42. Input/Output Slave Mapping Window n Base—Offset: 0x10400, 0x10410, 0x10420, 0x10430, 0x10440,

0x10450, 0x10460, 0x10470, 0x10480, 0x10490, 0x104A0, 0x104B0, 0x104C0, 0x104D0, 0x104E0, 0x104F0

Field

Bits

Access

Function

Default

BASE

[31:3] RW

Start of the Avalon-MM address window to be mapped. The

three least significant bits of the 32-bit base are assumed to be

all zeros.

29'h0

RSRV

[2:0]

RO

Reserved

3'h0

Table 6–43. Input/Output Slave Mapping Window n Mask—Offset: 0x10404, 0x10414, 0x10424, 0x10434, 0x10444,

0x10454, 0x10464, 0x10474, 0x10484, 0x10494, 0x104A4, 0x104B4, 0x104C4, 0x104D4, 0x104E4, 0x104F4

Field

Bits

Access

Function

Default

MASK

[31:3] RW

29 most significant bits of the mask for the address mapping

window. The three least significant bits of the 32-bit mask are

assumed to be zeros.

29'h0

WEN

[2]

RW

Window enable. Set to one to enable the corresponding

window.

1'b0

RSRV

[1:0]

RO

Reserved

2'h0

Table 6–44. Input/Output Slave Mapping Window n Offset—Offset: 0x10408, 0x10418, 0x10428, 0x10438, 0x10448,

0x10458, 0x10468, 0x10478, 0x10488, 0x10498, 0x104A8, 0x104B8, 0x104C8, 0x104D8, 0x104E8, 0x104F8

Field

Bits

Access

Function

Default

OFFSET

[31:3] RW

Bits [31:3] of the starting offset into the RapidIO address

space. The three least significant bits of the 34-bit offset are

assumed to be zeros.

29'h0

RSRV

[2]

RO

Reserved

1'b0

XAMO

[1:0]

RW

Extended Address: two most significant bits of the 34-bit

offset.

2'h0