Altera RapidIO MegaCore Function User Manual

Page 81

Chapter 4: Functional Description

4–35

Logical Layer Modules

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

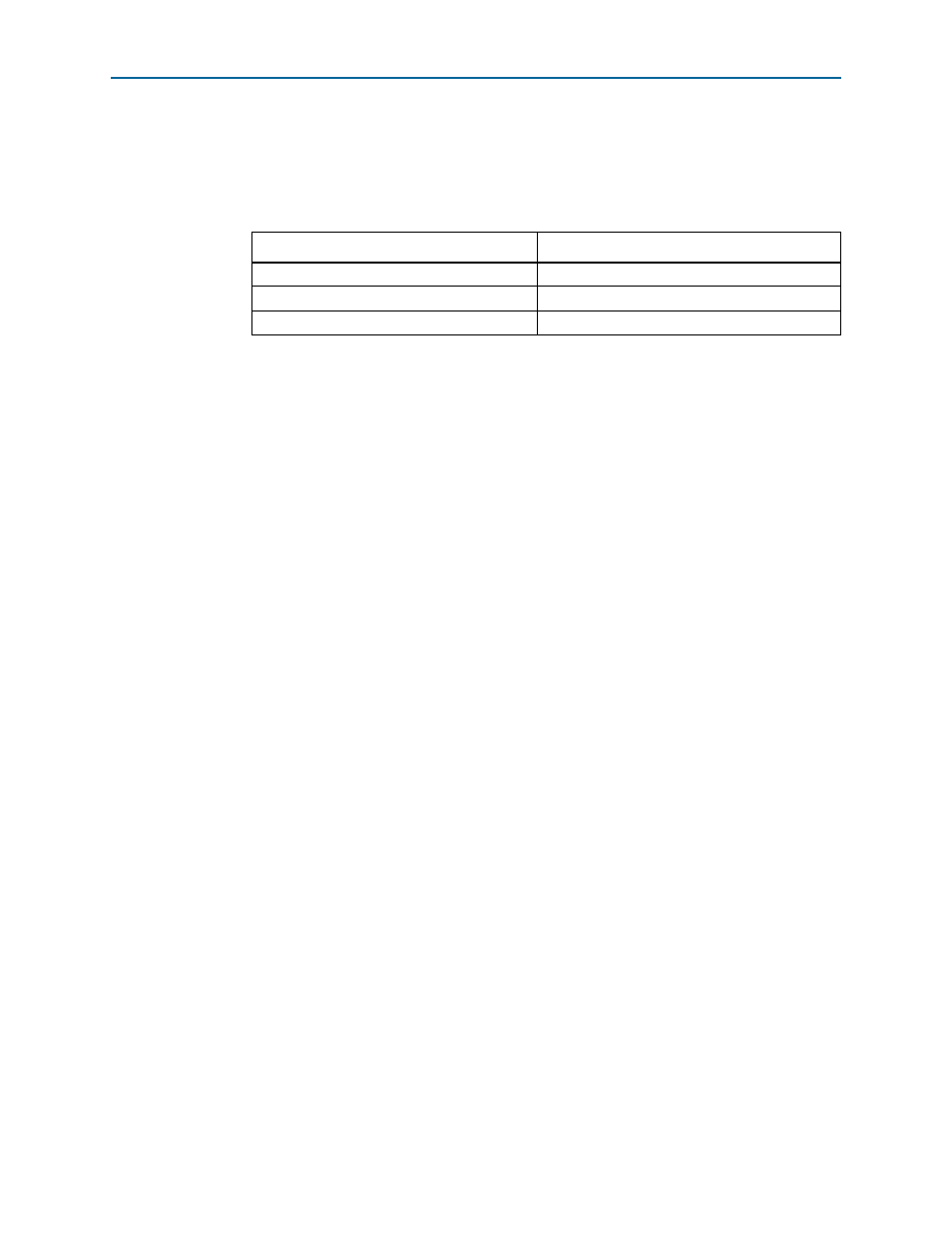

Input/Output Avalon-MM Master Address Mapping Windows

Address mapping or translation windows are used to map windows of 34-bit

RapidIO addresses into windows of 32-bit Avalon-MM addresses.

lists the

registers used for address translation.

Your variation must have at least one translation window. Arria 10 variations have 16

address translation windows. You can change the values of the window defining

registers at any time. You should disable a window before changing its window

defining registers.

A window is enabled if the window enable (WEN) bit of the I/O Master Mapping

Window n Mask

register is set.

The number of mapping windows is defined by the Number of receive address

translation windows

parameter, which supports up to 16 sets of registers. Each set of

registers supports one address mapping window.

For each window that is defined and enabled, the least significant bits of the incoming

RapidIO address are masked out by the window mask and the resulting address is

compared to the window base. If the addresses match, the Avalon-MM address is

made of the least significant bits of the RapidIO address and the window offset using

the following equation:

Let rio_addr[33:0] be the 34-bit RapidIO address, and address[31:0] the local

Avalon-MM address.

Let base[31:0], mask[31:0] and offset[31:0] be the three window-defining

registers. The least significant three bits of these registers are always 3’b000.

Starting from window 0, for the first window in which

((rio_addr

& {xamm, mask}) == ({xamb, base} & {xamm, mask}),

where xamm and xamb are the Extended Address MSB fields of the I/O Master Mapping

Window

n Mask and the I/O Master Mapping Window n Base registers, respectively,

let address[31:3] = (offset[31:3] & mask[31:3]) |

(rio_addr[31:3]

& ~mask[31:3])

The value of address[2] is zero for variations with 64-bit wide datapath Avalon-MM

interfaces.

The value of address[2] is determined by the values of wdptr and rdsize or wrsize

for variations with 32-bit wide datapath Avalon-MM interfaces.

The value of address[1:0] is always zero.

For each received NREAD or NWRITE_R request packet that does not match any enabled

window, an ERROR response packet is returned.

Table 4–6. Address Translation Registers

Registers

Location

Input/Output master base address

Input/Output master address mask

Input/Output master address offset