Altera RapidIO MegaCore Function User Manual

Page 24

2–2

Chapter 2: Getting Started

Files Generated for Altera IP Cores (Legacy Parameter Editor)

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

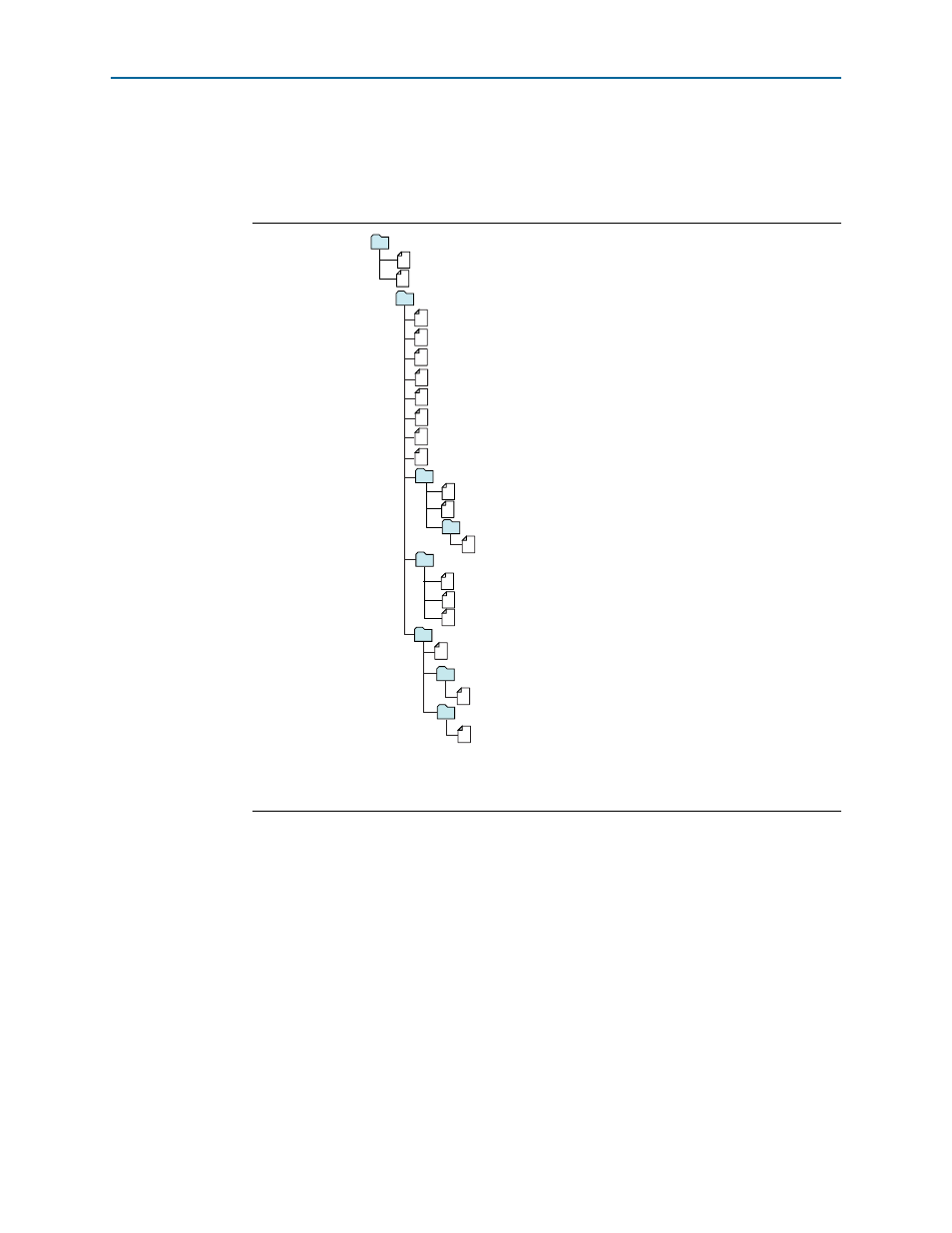

Files Generated for Altera IP Cores (Legacy Parameter Editor)

The Quartus II software version 14.0 and previous parameter editor generates the

following output file structure for Altera IP cores:

In the case of the non-Arria 10 RapidIO IP core, the testbench scripts for the different

simulators appear in <your_ip>/simulation/<vendor> and the testbench and

simulation files appear in <your_ip>/simulation/submodules. The main testbench file

is <your_ip>/simulation/submodules/<variation_name>_rapidio_0_tb.v.

The Quartus II software generates the <your_ip>/testbench directory if you click

Generate > Generate Testbench

in the RapidIO parameter editor. However, the

resulting testbench is composed of BFM stubs and does not exercise the RapidIO IP

core in any meaningful way. The Altera-provided RapidIO IP core testbench

described in

is generated when you generate a simulation

model of the IP core. For non-Arria 10 variations, this testbench is available in

<your_ip>/simulation/submodules.

Figure 2–1. IP Core Generated Files (Legacy Parameter Editor)

Notes:

1. If supported and enabled for your IP variation

2. If functional simulation models are generated

<Project Directory>

<your_ip>_bb.v - Verilog HDL black box EDA synthesis file

<your_ip>_inst.v or .vhd - Sample instantiation template

synthesis - IP synthesis files

<your_ip>.qip - Lists files for synthesis

testbench - Simulation testbench files

1

<testbench_hdl_files>

<simulator_vendor> - Testbench for supported simulators

<simulation_testbench_files>

<your_ip>.v or .vhd - Top-level IP variation synthesis file

simulation - IP simulation files

<your_ip>.sip - NativeLink simulation integration file

<simulator vendor> - Simulator setup scripts

<simulator_setup_scripts>

<your_ip> - IP core variation files

<your_ip>.qip or .qsys - System or IP integration file

<your_ip>_generation.rpt - IP generation report

<your_ip>.bsf - Block symbol schematic file

<your_ip>.ppf - XML I/O pin information file

<your_ip>.spd - Combines individual simulation startup scripts

1

<your_ip>.html - Contains memory map

<your_ip>.sopcinfo - Software tool-chain integration file

<your_ip>_syn.v or .vhd - Timing & resource estimation netlist

1

<your_ip>.debuginfo - Lists files for synthesis

<your_ip>.v, .vhd, .vo, .vho - HDL or IPFS models

2

<your_ip>_tb - Testbench for supported simulators

<your_ip>_tb.v or .vhd - Top-level HDL testbench file