Maintenance interrupt control registers, Maintenance interrupt control registers –16, Rammed in the – Altera RapidIO MegaCore Function User Manual

Page 148: Base device id csr—offset: 0x60, Table 6–26, In which the, Table 6–25

6–16

Chapter 6: Software Interface

Transport and Logical Layer Registers

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

Maintenance Interrupt Control Registers

describe the registers that relate to the Maintenance module

interrupts. If any of these error conditions are detected and if the corresponding

Interrupt Enable bit is set, the sys_mnt_s_irq signal is asserted.

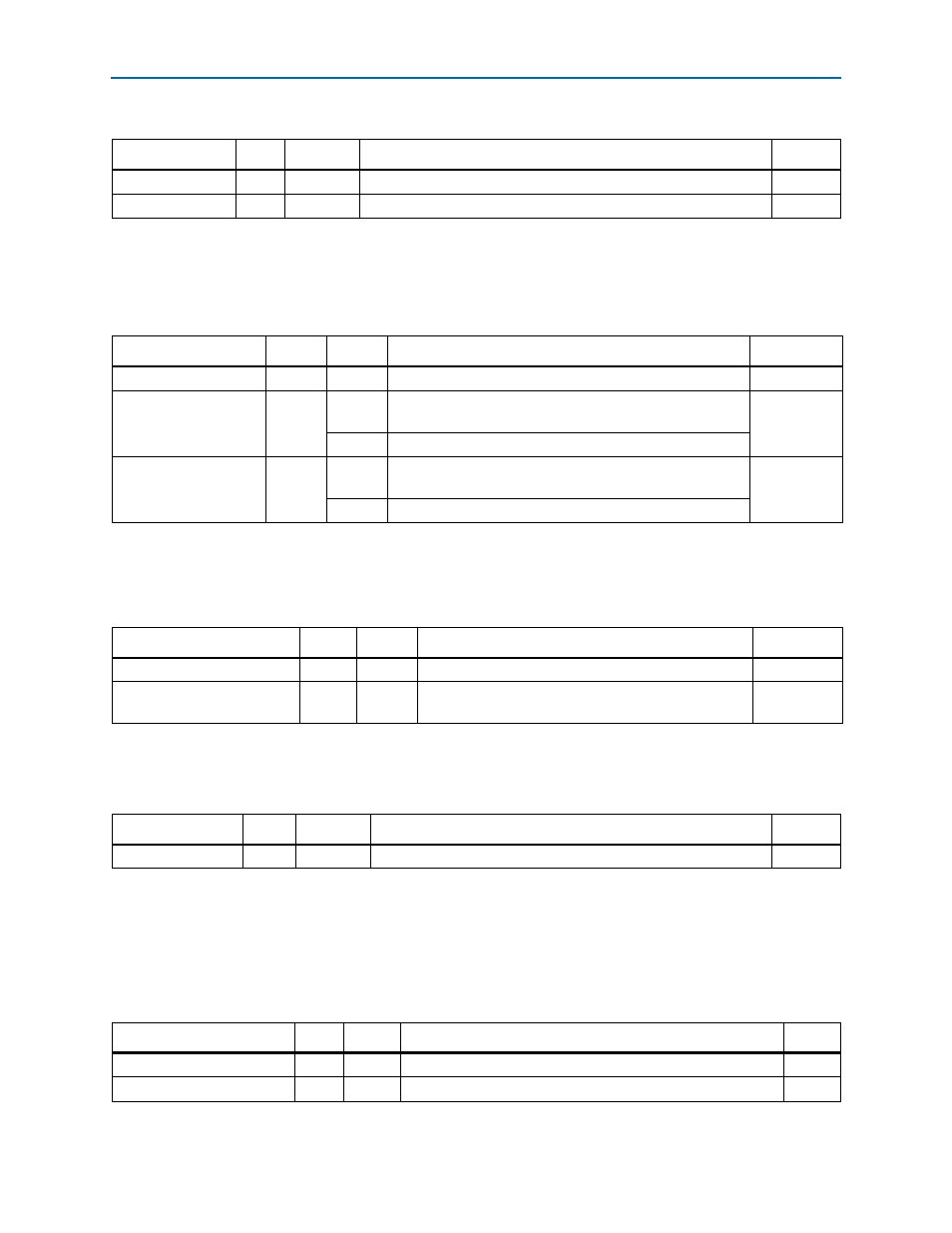

Table 6–22. Local Configuration Space Base Address 1 CSR—Offset: 0x5C

Field

Bits

Access

Function

Default

LCSBA

[31]

RO

Reserved for a 34-bit local physical address

1'b0

LCSBA

[30:0] RW

Bits 33:4 of a 34-bit physical address

31'h0

Note to

:

(1) The Local Configuration Space Base Address registers are hard coded to zero. If the Input/Output Avalon-MM master interface is connected to

the System Maintenance Avalon-MM slave interface, regular read and write operations rather than MAINTENANCE operations, can be used to

access the processing element's registers for configuration and maintenance.

Table 6–23. Base Device ID CSR—Offset: 0x60

Field

Bits

Access

Function

Default

RSRV

[31:24]

RO

Reserved

8'h0

DEVICE_ID

[23:16]

RW

This is the base ID of the device in a small common

transport system.

8'hFF

RO

Reserved if the system does not support 8-bit device ID.

LARGE_DEVICE_ID

[15:0]

RW

This is the base ID of the device in a large common transport

system.

16'hFFFF

RO

Reserved if the system does not support 16-bit device ID.

Note to

:

(1) In a small common transport system, the DEVICE_ID field is Read-Write and the LARGE_DEVICE_ID field is Read-only. In a large common

transport system, the DEVICE_ID field is Read-only and the LARGE_DEVICE_ID field is Read-Write.

Table 6–24. Host Base Device ID Lock CSR—Offset: 0x68

Field

Bits

Access

Function

Default

RSRV

[31:16]

RO

Reserved

16'h0

HOST_BASE_DEVICE_ID

[15:0]

RW

This is the base device ID for the processing element

that is initializing this processing element.

16'hFFFF

Note to

:

(1) Write once; can be reset. See Part 3 §3.5.2 of the RapidIO Specification Rev 2.1 for more information.

Table 6–25. Component Tag CSR—Offset: 0x6C

Field

Bits

Access

Function

Default

COMPONENT_TAG

[31:0]

RW

This is a component tag for the processing element.

32'h0

Table 6–26. Maintenance Interrupt—Offset: 0x10080 (Part 1 of 2)

Field

Bits

Access

Function

Default

RSRV

[31:7] RO

Reserved

25'h0

PORT_WRITE_ERROR

[6]

RW1C

Port-write error

1'b0