Input/output slave interrupts, Input/output slave interrupts –22, That – Altera RapidIO MegaCore Function User Manual

Page 154: Table 6–46 on, Ns in

6–22

Chapter 6: Software Interface

Transport and Logical Layer Registers

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

Input/Output Slave Interrupts

describe the available Input/Output slave interrupts and

corresponding interrupt enable bits. These interrupt bits assert the sys_mnt_s_irq

signal if the corresponding interrupt bit is enabled.

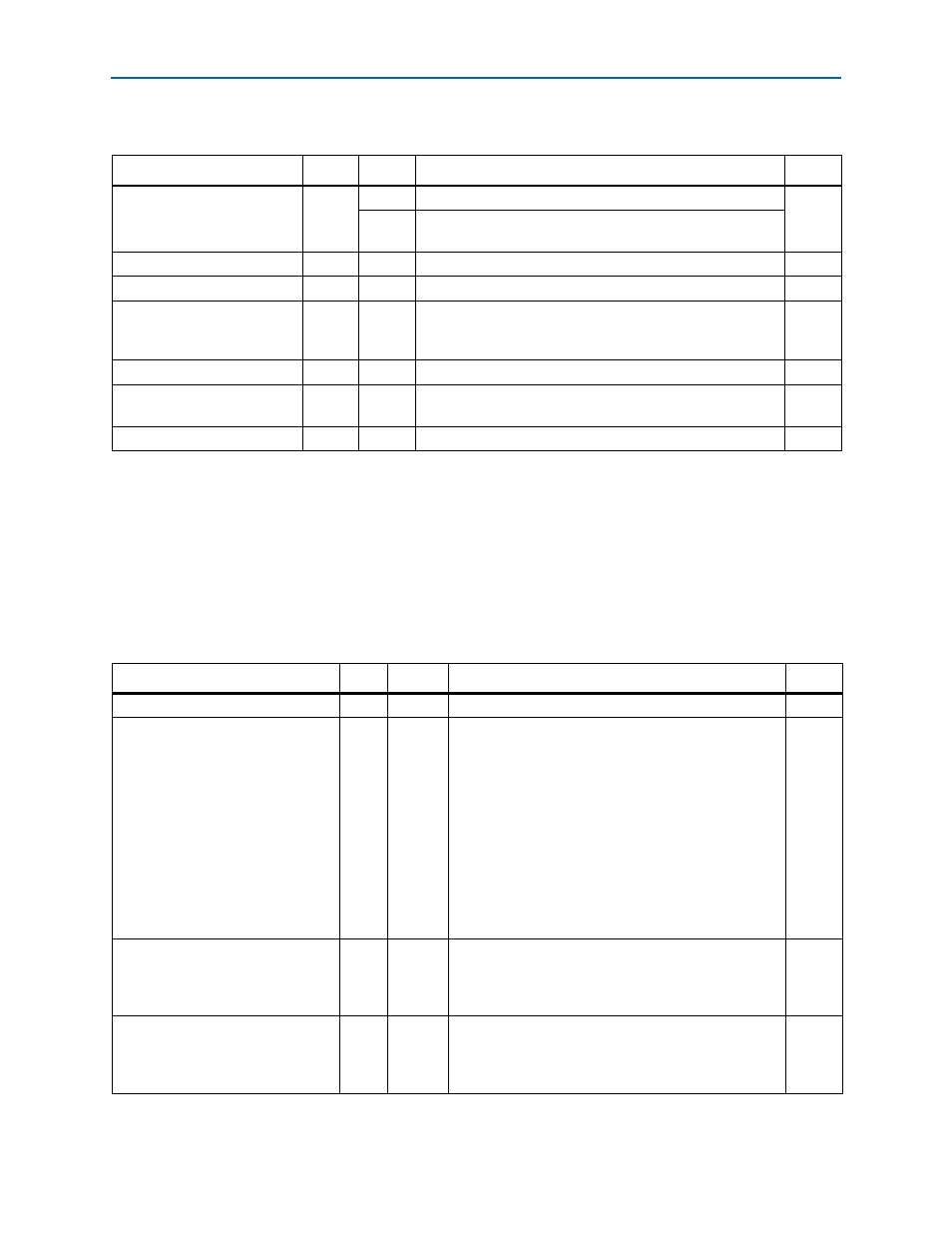

Table 6–45. Input/Output Slave Mapping Window n Control—Offset: 0x1040C, 0x1041C, 0x1042C, 0x1043C, 0x1044C,

0x1045C, 0x1046C, 0x1047C, 0x1048C, 0x1049C, 0x104AC, 0x104BC, 0x104CC, 0x104DC, 0x104EC, 0x104FC

Field

Bits

Access

Function

Default

LARGE_DESTINATION_ID

(MSB)

[31:24]

RO

Reserved if the system does not support 16-bit device ID.

8'h0

RW

MSB of the Destination ID if the system supports 16-bit

device ID.

DESTINATION_ID

[23:16] RW

Destination ID

8'h0

RSRV

[15:8]

RO

Reserved

8'h0

PRIORITY

[7:6]

RW

Request Packet’s priority 2’b11 is not a valid value for the

priority

field. Any attempt to write 2’b11 to this field is

overwritten with 2’b10.

2'h0

RSRV

[5:2]

RO

Reserved

4'h0

SWRITE_ENABLE

[1]

RW

SWRITE enable. Set to one to generate SWRITE request

packets.

1'b0

NWRITE_R_ENABLE

[0]

RW

NWRITE_R enable

1'b0

:

(1) Bits 0 and 1 (NWRITE_R_ENABLE and SWRITE_ENABLE) are mutually exclusive. An attempt to write ones to both of these fields at the same time

is ignored, and that part of the register keeps its previous value.

Table 6–46. Input/Output Slave Interrupt—Offset: 0x10500 (Part 1 of 2)

Field

Bits

Access

Function

Default

RSRV

[31:5] RO

Reserved

27'h0

NWRITE_RS_COMPLETED

[4]

RW1C

Indicates no pending NWRITE_R transactions remain in

the RapidIO IP core. Set when the

PENDING_NWRITE_RS

field of the Input/Output

Slave Pending NWRITE_R Transactions

register

(offset 0x10508) is set to 0. Because of the inherent

delay in incrementing the PENDING_NWRITE_RS field

after the start of the corresponding write transaction on

the Avalon-MM interface, you should wait at least 8

Avalon clock cycles after the start of the NWRITE_R

transaction whose completion you wish to trigger an

interrupt, before you clear this bit and enable this

interrupt.

1'b0

INVALID_WRITE_BYTEENABLE

[3]

RW1C

Write byte enable invalid. Asserted when

io_s_wr_byteenable

is set to invalid values. For

information about valid values see

and

1'b0

INVALID_WRITE_BURSTCOUNT

[2]

RW1C

Write burst count invalid. Asserted when

io_s_wr_burstcount

is set to an odd number larger

than one in variations with 32-bit wide datapath Avalon-

MM write interfaces.

1'b0