Table 6–4 – Altera RapidIO MegaCore Function User Manual

Page 137

Chapter 6: Software Interface

6–5

Physical Layer Registers

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

0x158

ERRSTAT

Port 0 Error and Status CSR

0x15C

PCTRL0

Port 0 Control CSR

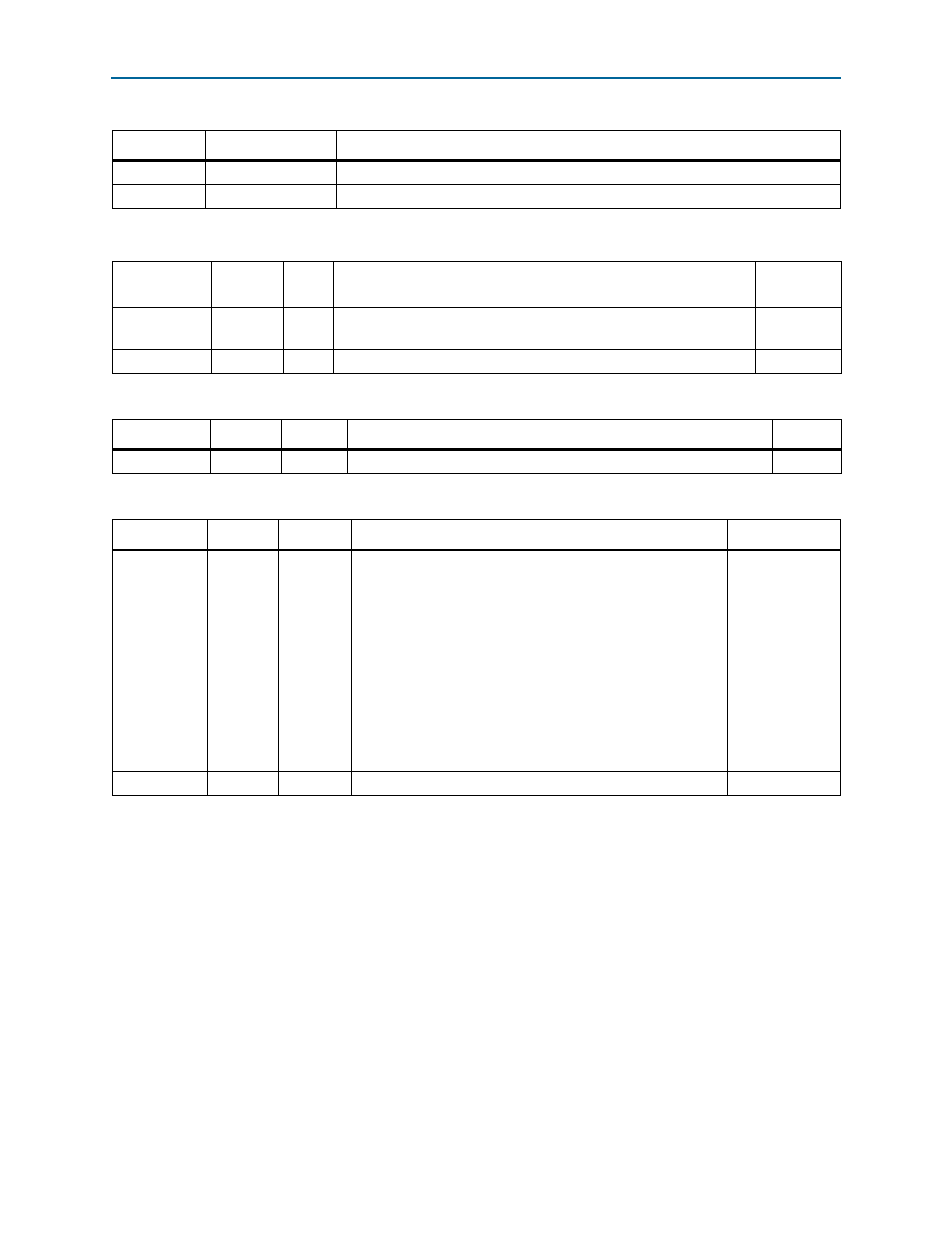

Table 6–3. Physical Layer Register Map (Part 2 of 2)

Address

Name

Description

Table 6–4. PHEAD0—LP-Serial Register Block Header—0x100

Field Bits

Acces

s

Function Default

EF_PTR

[31:16] RO

Hard-wired pointer to the next block in the data structure, if one exists.

The value is set from the ef_ptr input port.

ef_ptr

EF_ID

[15:0]

RO

Hard-wired extended features ID.

16'h0001

Table 6–5. PHEAD1—Reserved Register—0x104

Field Bits

Access

Function

Default

RSRV

[31:0] UR0

Reserved

32’h0

Table 6–6. PLTCTRL—Port Link Time-Out Control CSR—0x120

Field Bits

Access

Function

Default

VALUE

[31:8] RW

Time-out interval value for link-layer event pairs such as the

time interval between sending a packet and receiving the

corresponding acknowledge control symbol, or between

sending a link-request and receiving the corresponding

link-response.

The duration of the link-response time-out is approximately

equal to 4.5 seconds multiplied by the contents of this field,

divided by (2

24

- 1).

Note: Avoid time-out values less than 0x000010 because they

may not be reliable.

24'hFF_FFFF

RSRV

[7:0] UR0

Reserved

8’h0