Altera RapidIO MegaCore Function User Manual

Page 92

4–46

Chapter 4: Functional Description

Logical Layer Modules

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

Input/Output Slave Translation Window Example

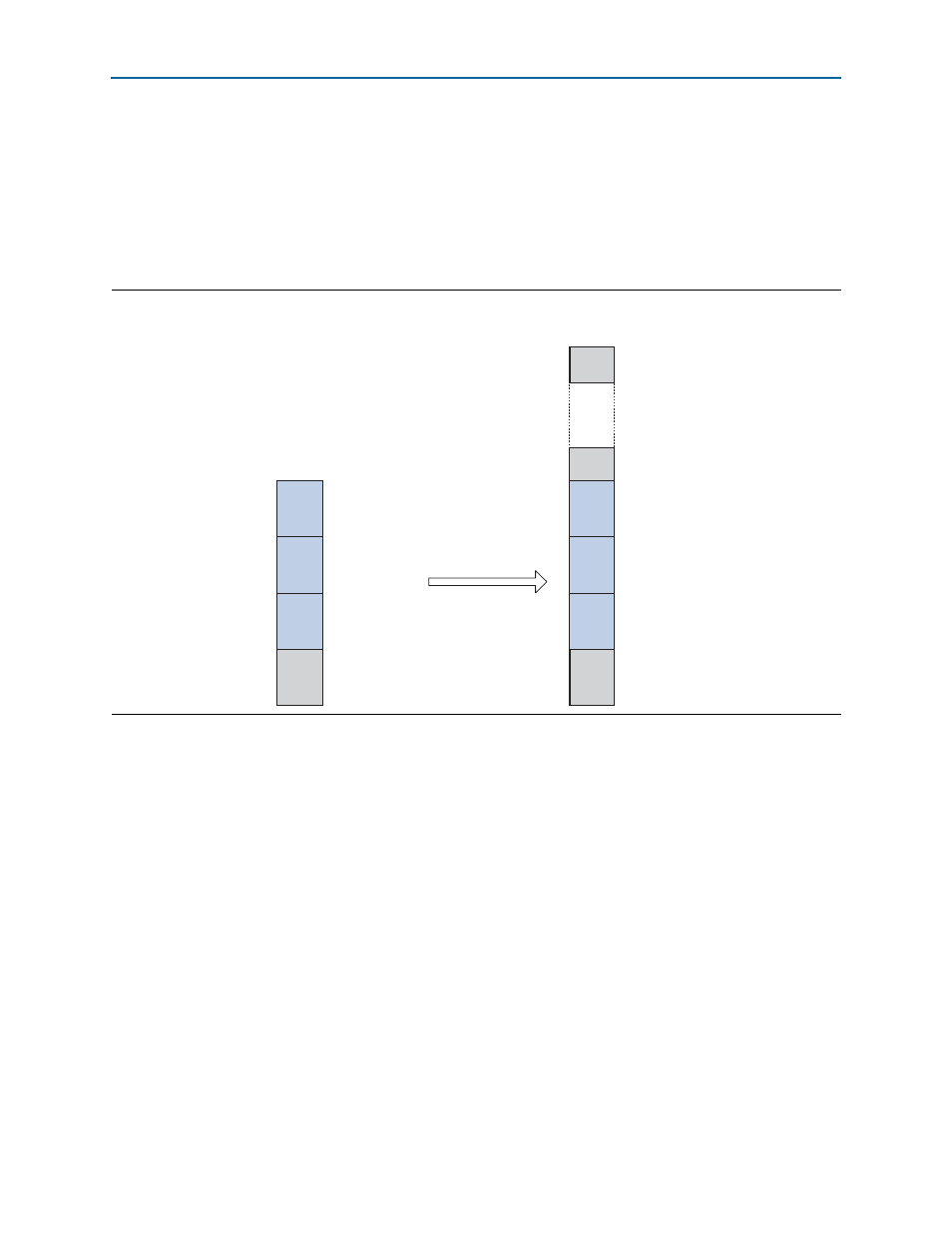

This section contains an example illustrating the use of I/O slave translation

windows. In this example, a RapidIO IP core with 8-bit device ID communicates with

three other processing endpoints through three I/O slave translation windows. For

this example, the XAMO bits are set to 2'b00 for all three windows. The offset value

differs for each window, which results in the segmentation of the RapidIO address

space that is shown in

The two most significant bits of the Avalon-MM address are used to differentiate

between the processing endpoints.

through

show the address

translation implemented for each window. Each figure shows the value for the

destination ID of the control register for one window.

Translation Window 0

An Avalon-MM address in which the two most significant bits have the value 2'b01

matches window 0. The RapidIO transaction corresponding to the Avalon-MM

operation has a DESTINATION_ID value of 0x55. This value corresponds to processing

endpoint 0.

Figure 4–23. Input/Output Slave Translation Window Address Mapping

0x00000000

0x3FFFFFFC

0xFFFFFFFC

0x40000000

Avalon-MM

Address Space

RapidIO

Address Space

0x7FFFFFFC

0x80000000

0xBFFFFFFC

0xC0000000

0x000000000

0x03FFFFFF8

0x040000000

0x07FFFFFF8

0x080000000

0x0BFFFFFF8

0x0C0000000

0x0FFFFFFF8

0x100000000

0x3FFFFFFF8

PE 2

PE 1

PE 0

PE 0

PE 1

PE 2