Maintenance write and read transactions, Maintenance write and read transactions –4 – Altera RapidIO MegaCore Function User Manual

Page 166

7–4

Chapter 7: Testbenches

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

Read and write tasks that are defined in the BFM instance, bfm_cnt_master, program

the DUT’s registers. Read and write tasks defined in the BFM instance

sister_bfm_cnt_master program the sister_rio module’s registers. For the exact

parameters passed to these tasks, refer to the file

either a write or read transaction across the System Maintenance Avalon-MM slave

interface.

In the configuration shown in

, the IP cores can exchange basic

packets across the serial link.

Maintenance Write and Read Transactions

If the Maintenance module is present, the testbench sends a few MAINTENANCE read

and write request packets from the DUT to the sister_rio module. Transactions are

initiated by Avalon-MM transactions on the DUT's Maintenance Avalon-MM slave

interface, and are checked on the sister_rio’s Maintenance Avalon-MM master

interface.

The first set of tests performed are MAINTENANCE write and read requests. The DUT

sends two MAINTENANCE write requests to the sister_rio module. The writes are

performed by running the rw_addr_data task defined inside the BFM instance,

bfm_mnt_master. The bfm_mnt_master is an instance of the module

avalon_bfm_master, defined in the file

following parameters are passed to the task:

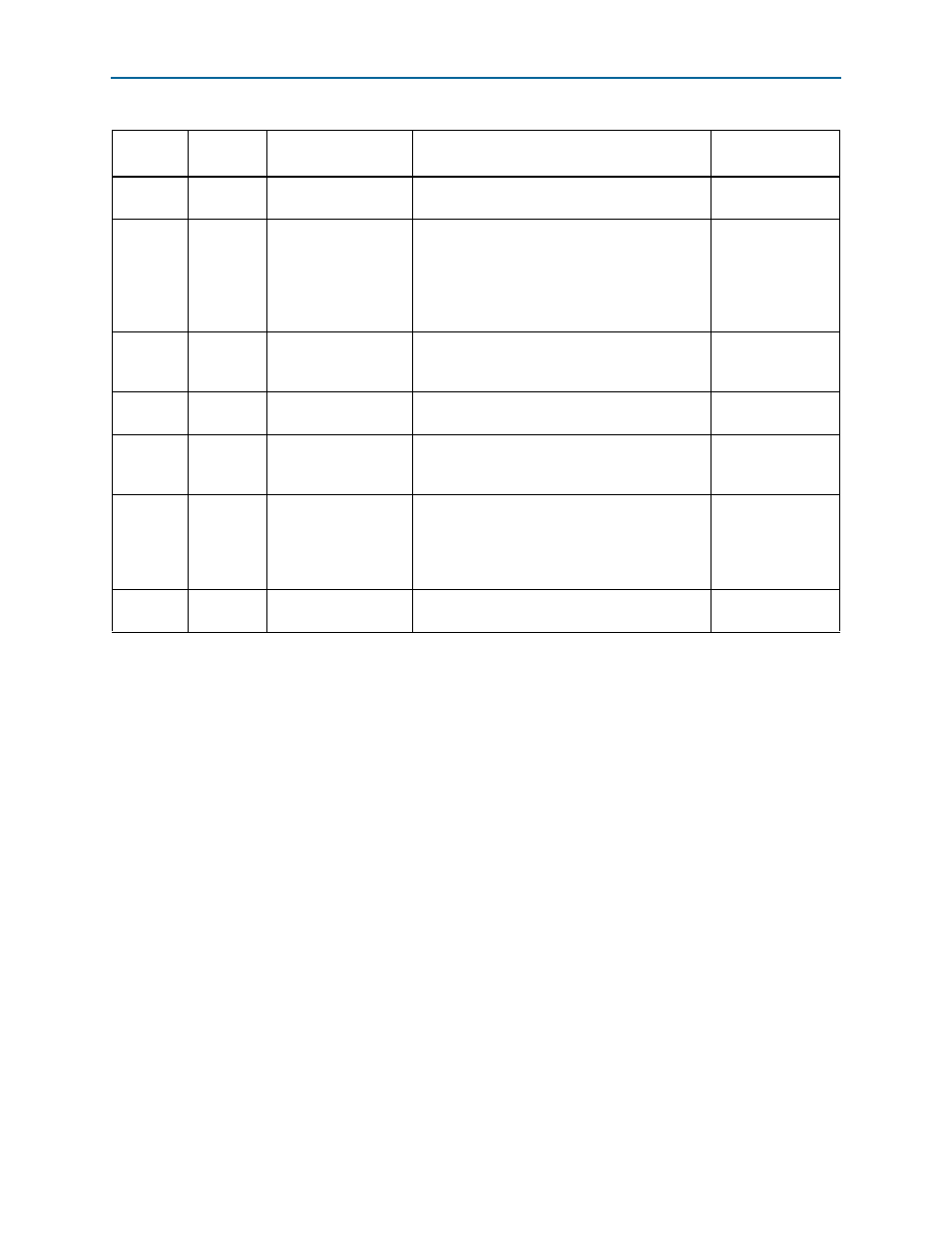

sister_rio

0x0013C

General

Control

CSR

Enable Request packet generation by the

sister_rio module.

32'h6000_0000

rio

0x1040C

Input/Output

Slave

Window

0 Control

Set the DESTINATION_ID for outgoing

transactions to a value 0x55 or 0x5555. The

width of the DESTINATION_ID field depends on

the sister_rio device ID width. This value

matches the base device ID of the sister_rio

module.

32'h0055_0000

or

32'h5555_0000

rio

0x10404

Input/Output

Slave

Window

0 Mask

Define the Input/Output Avalon-MM Slave

Window

0 to cover the whole address space

(mask set to all zeros) and enable it.

32'h0000_0004

sister_rio

0x10504

Input/Output

Slave

Interrupt Enable

Enable the I/O slave interrupts.

32'h0000_000F

sister_rio

0x10304

Input/Output

Master

Window 0

Mask

Enable the sister_rio I/O Master Window 0,

which allows the sister_rio to receive I/O

transactions.

32'h0000_0004

rio

0x1010C

TX Maintenance

Window

0 Control

Set the DESTINATION_ID for outgoing

MAINTENANCE

packets to 0x55 or 0x5555,

depending on the sister_rio device ID width. This

value matches the base device ID of the sister_rio

module. Set the hop count to 0xFF.

32'h0055_FF00

or 32'h5555_FF00

rio

0x10104

TX

Maintenance

Window

0 Mask

Enable the TX Maintenance window 0.

32'h0000_0004

Table 7–1. Testbench Registers (Part 2 of 2)

Module

Register

Address

Register Name

Description

Value