Table 6–7 on, Table 6–7 – Altera RapidIO MegaCore Function User Manual

Page 138

6–6

Chapter 6: Software Interface

Physical Layer Registers

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

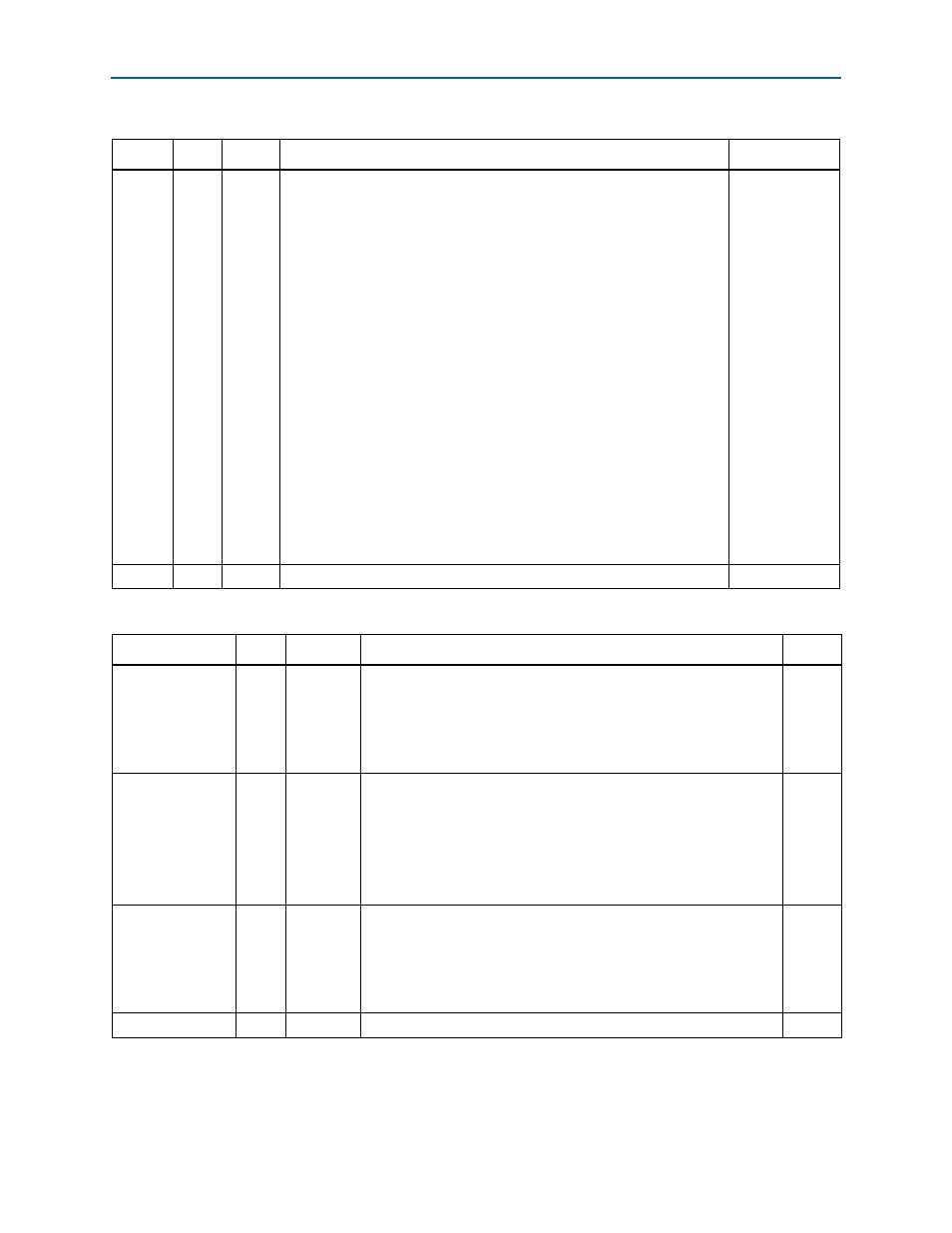

Table 6–7. PRTCTRL—Port Response Time-Out Control CSR—0x124

Field Bits

Access

Function

Default

VALUE

[31:8] RW

Time-out internal value.

■

Physical layer-only variations: This value is not used by the RapidIO IP

core. The contents of this register drive the port_response_timeout

output signal.

■

Variations using Logical layers: The duration of the port response

time-out for all transactions that require a response—including

MAINTENANCE

, DOORBELL, NWRITE_R, and NREAD transactions—is

approximately equal to 4.5 seconds multiplied by the contents of this

field, divided by (2

24

- 1).

Note: Avoid time-out values less than 0x000010 because they may not

be reliable.

Note: A new value in this field might not propagate quickly enough to be

applied to the next transaction. Any packet sent within 64 Avalon clock

cycles of the value change in the register might be sent using the

previous time-out value.

Note: Avoid changing the value in this field when any packet is waiting to

be transmitted or waiting for a response, to ensure that in each FIFO, the

pending entries all have the same time-out value.

24'hFF_FFFF

RSRV

[7:0] UR0

Reserved

8'h0

Table 6–8. Port General Control—Offset: 0x13C

Field

Bits

Access

Function

Default

HOST

[31]

RW

A host device is a device that is responsible for system exploration,

initialization, and maintenance. Host devices typically initialize agent or

slave devices.

'b0 - agent or slave device

'b1 - host device

1'b0

ENA

[30]

RW

The Master Enable bit controls whether or not a device is allowed to

issue requests to the system. If Master Enable is not set, the device

may only respond to requests.

'b0 - The processing element cannot issue requests

'b1 - The processing element can issue requests

Variations that use only the Physical layer ignore this bit.

1'b0

DISCOVER

[29]

RW

This device has been located by the processing element responsible

for system configuration.

'b0 - The device has not been previously discovered

'b1 - The device has been discovered by another processing

element

1'b0

RSRV

[28:0]

RO

Reserved

29'b0