Table 4–8, For inf – Altera RapidIO MegaCore Function User Manual

Page 84

4–38

Chapter 4: Functional Description

Logical Layer Modules

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

lists the allowed write-request conversions for RapidIO IP core 1x

variations.

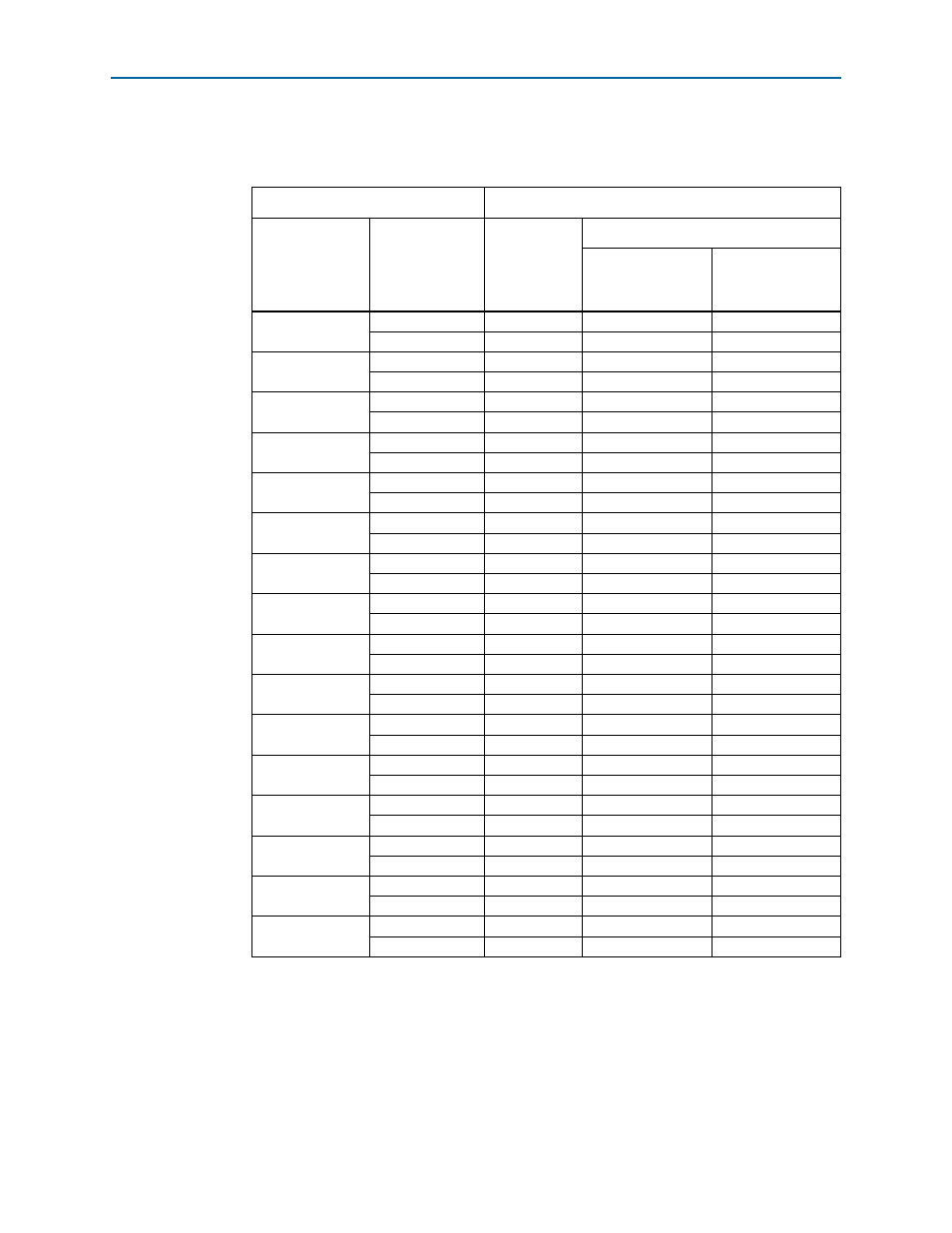

Table 4–8. RapidIO Master Write Transaction Burstcount and Byteenable (32-Bit Datapath)

RapidIO Values

Avalon-MM Values

wrsize

(4'bxxxx)

wdptr

(1'bx)

Maximum

Burstcount

Byteenable (8’b0000xxxx)

First Cycle

or

All Cycles

Second Cycle

(If Different)

0000

0

1

1000

—

1

1

1000

—

0001

0

1

0100

—

1

1

0100

—

0010

0

1

0010

—

1

1

0010

—

0011

0

1

0001

—

1

1

0001

—

0100

0

1

1100

—

1

1

1100

—

0101

1

1110

—

1

0111

—

0110

0

1

0011

—

1

1

0011

—

0111

0

2

1000

1111

1

2

1111

0001

1000

0

1

1111

—

1

1

1111

—

1001

0

2

1100

1111

1

2

1111

0011

1010

2

1110

1111

2

1111

0111

1011

0

2

1111

1111

1

4

1111

—

1100

0

8

1111

—

1

16

1111

—

1101

—

—

—

1

32

1111

—

1110

—

—

—

—

—

—

1111

—

—

—

1

64

1111

—

Notes to

(1) If the maximum burst count is larger than 2, the actual burst count depends on the size of the payload in the

received request packet.

(2) This combination of wdptr and wrsize values should be avoided, because the resulting byteenable value is not

allowed by the Avalon-MM specification.

(3) This combination of wdptr and wrsize values is reserved. If this combination is received, the RapidIO IP core

declares an error.