Altera RapidIO MegaCore Function User Manual

Page 86

4–40

Chapter 4: Functional Description

Logical Layer Modules

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

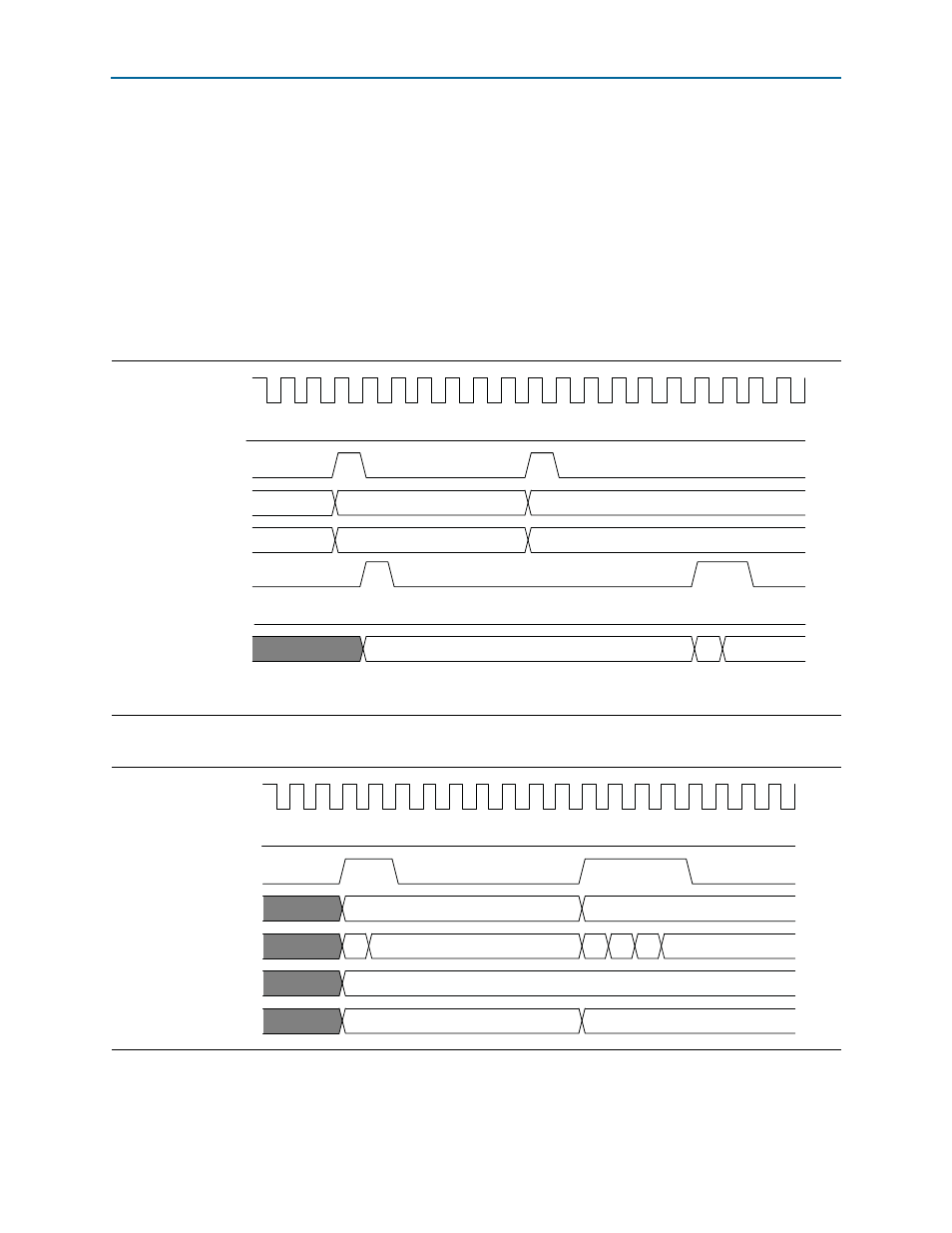

Input/Output Avalon-MM Master Module Timing Diagrams

shows the timing dependencies on the Avalon-MM master interface for

an incoming RapidIO NREAD transaction.

shows the timing dependencies

on the Avalon-MM master interface for an incoming RapidIO NWRITE transaction.

Both transaction requests are received on the RapidIO link and sent on to the Logical

layer Avalon-MM master module. If the RapidIO link partner is also an Altera

RapidIO IP core, the timing diagrams in

“Input/Output Avalon-MM Slave Module

show the same transactions as they originate on the

Avalon-MM interface of the RapidIO link partner’s Input/Output Avalon-MM slave

module.

Figure 4–19. NREAD Transaction on the Input/Output Avalon-MM Master Interface

sysclk

io_m_rd_waitrequest

io_m_rd_read

io_m_rd_address[31:0]

io_m_rd_readdatavalid

io_m_rd_readerror

io_m_rd_readdata[31:0]

io_m_rd_burstcount[7:0]

00000000

Adr0

Adr1

r0

r1

r2

00

01

02

Figure 4–20. NWRITE Transaction on the Input/Output Avalon-MM Master Interface

sysclk

io_m_wr_waitrequest

io_m_wr_write

io_m_wr_address[31:0]

io_m_wr_writedata[31:0]

io_m_wr_byteenable[3:0]

io_m_wr_burstcount[7:0]

AdrA

AdrB

w1

w2

w3

w4

w5

w0

F

02

04