Table 1–7 – Altera RapidIO MegaCore Function User Manual

Page 18

1–10

Chapter 1: About This MegaCore Function

Performance and Resource Utilization

RapidIO MegaCore Function

August 2014

Altera Corporation

User Guide

shows the recommended device family speed grades for the Arria 10,

Arria V, Cyclone V, and Stratix V device families.

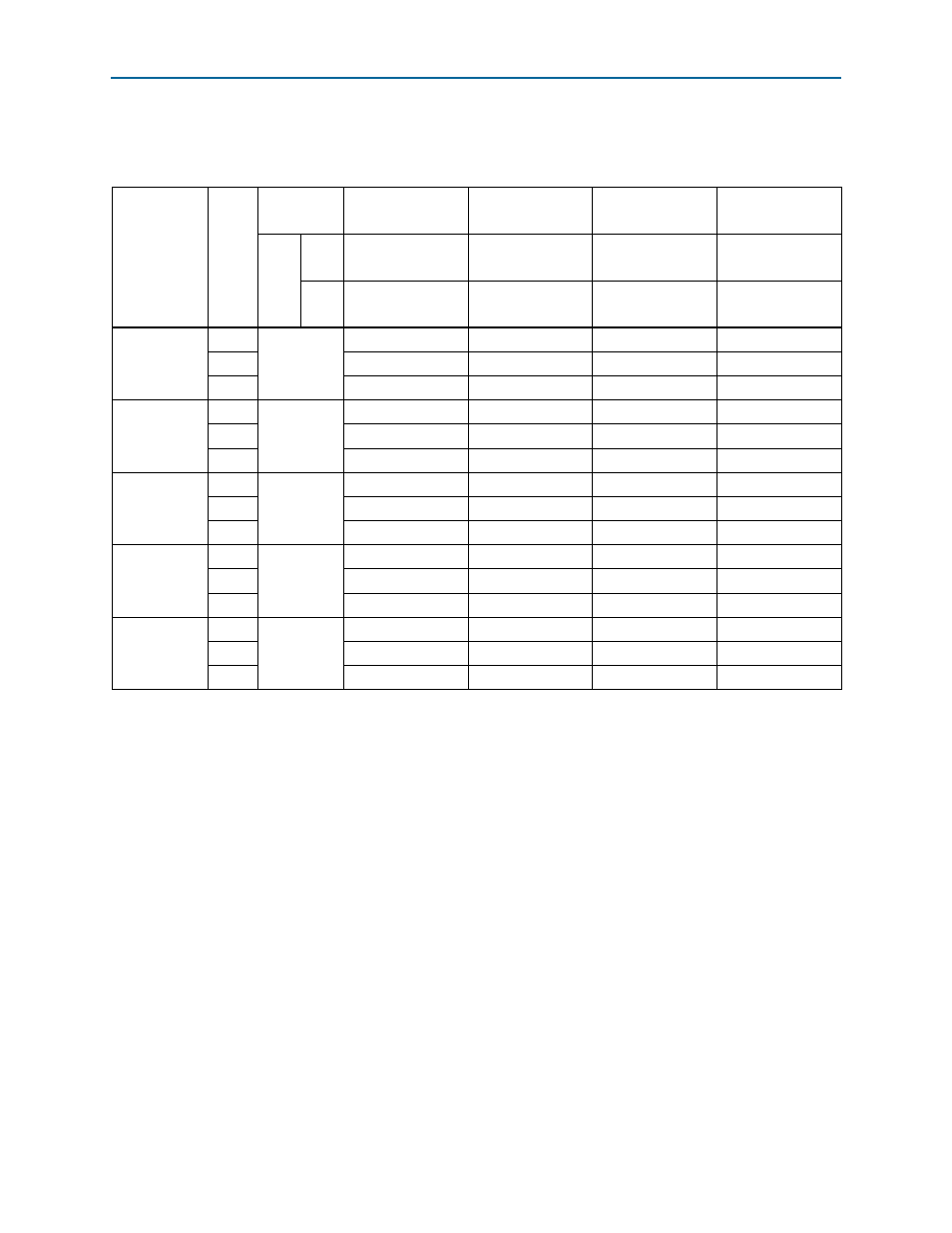

Table 1–7. Recommended Device Family Speed Grades for Newer Devices

Device

Family

Mode

Rate

1.25 Gbaud

2.5

Gbaud

3.125 Gbaud

5.0

Gbaud

f

MAX

1x,

2x

31.25 MHz

62.50 MHz

78.125 MHz

125

MHz

4x

62.5

MHz

125

MHz

156.25 MHz

250

MHz

Arria 10

1x

-1, -2, -3

-1, -2, -3

-1, -2, -3

-1, -2

2x

-1, -2, -3

-1, -2, -3

-1, -2, -3

-1, -2

4x

-1, -2, -3

-1, -2, -3

-1, -2, -3

-1, -2

Arria V (GX,

GT, SX, ST)

1x

C4, -5, C6

C4, -5, C6

C4, -5, C6

2x

C4, -5, C6

C4, -5, C6

C4, -5, C6

C4, -5

4x

C4, -5, C6

C4, -5

C4

Arria V GZ

1x

-3, -4

-3, -4

-3, -4

-3

2x

-3, -4

-3, -4

-3, -4

-3, -4

4x

-3, -4

-3, -4

-3, -4

-3

Stratix V

1x

C1, -2, -3, -4

C1, -2, -3, -4

C1, -2, -3, -4

C1, -2, -3

2x

C1, -2, -3, -4

C1, -2, -3, -4

C1, -2, -3, -4

C1, -2, -3, -4

4x

C1, -2, -3, -4

C1, -2, -3, -4

C1, -2, -3, -4

C1, -2, -3

Cyclone V

(GX, GT

,

SX, ST)

1x

C6, -7, C8

C6, -7, C8

C6, -7, C8

2x

C6, -7

C6, -7

C6, -7

-7

4x

C6, -7, C8

C6, -7

Notes to

(1) In this table, the entry -n indicates that both the industrial speed grade In and the commercial speed grade Cn are supported for this device

family, RapidIO mode, and baud rate.

(2) Some simple Arria V 1× variations with lane speed of 5.0 Gbaud, and some simple Arria V 4× variations with lane speeds of 3.125 Gbaud, such

as physical-layer-only variations,may meet timing in -5 speed grade devices, after following the Timing Advisor’s recommendations.

(3) Not supported for this device family.

(4) Altera recommends that for designs that include a 4× 5.0 Gbaud RapidIO IP core variation and that target a -3 speed grade Stratix V device, you

use multiple seeds in the Quartus II Design Space Explorer to find the optimal Fitter settings to meet the timing constraints. Following the Timing

Advisor's recommendations, including optimizing for speed and using LogicLock regions may be necessary to meet timing, especially for more

complex variations implemented in the largest devices.

(5) Only the -7 speed grade is available for Cyclone V GT devices.

(6) The RapidIO IP core supports 1× 5.0 Gbaud variations that target the Cyclone V device family in speed grade C7 Cyclone V GT devices only. The

RapidIO parameter editor does not warn you of this fact. You can generate a 1× 5.0 Gbaud variation that targets a Cyclone V GX variation, for

example, but when you attempt to add the extra constraints required for the RapidIO IP core, as discussed in

, the Quartus II software Analysis and Synthesis tool fails.

(7) The RapidIO IP core supports 2x 5.0 Gbaud variations that target the Cyclone V device family in Cyclone V GT devices only. The RapidIO

parameter editor does not warn you of this fact. You can generate a 2× 5.0 Gbaud variation that targets a Cyclone V GX variation, for example,

but when you attempt to add the extra constraints required for the RapidIO IP core, as discussed in

“Specifying Constraints” on page 2–8

Quartus II software Analysis and Synthesis tool fails.