Altera RapidIO MegaCore Function User Manual

Page 129

Chapter 5: Signals

5–15

Transport and Logical Layer Signals

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

describes the Avalon-ST pass-through receiver (Rx) signals.

f

For more information about these signals, refer to the

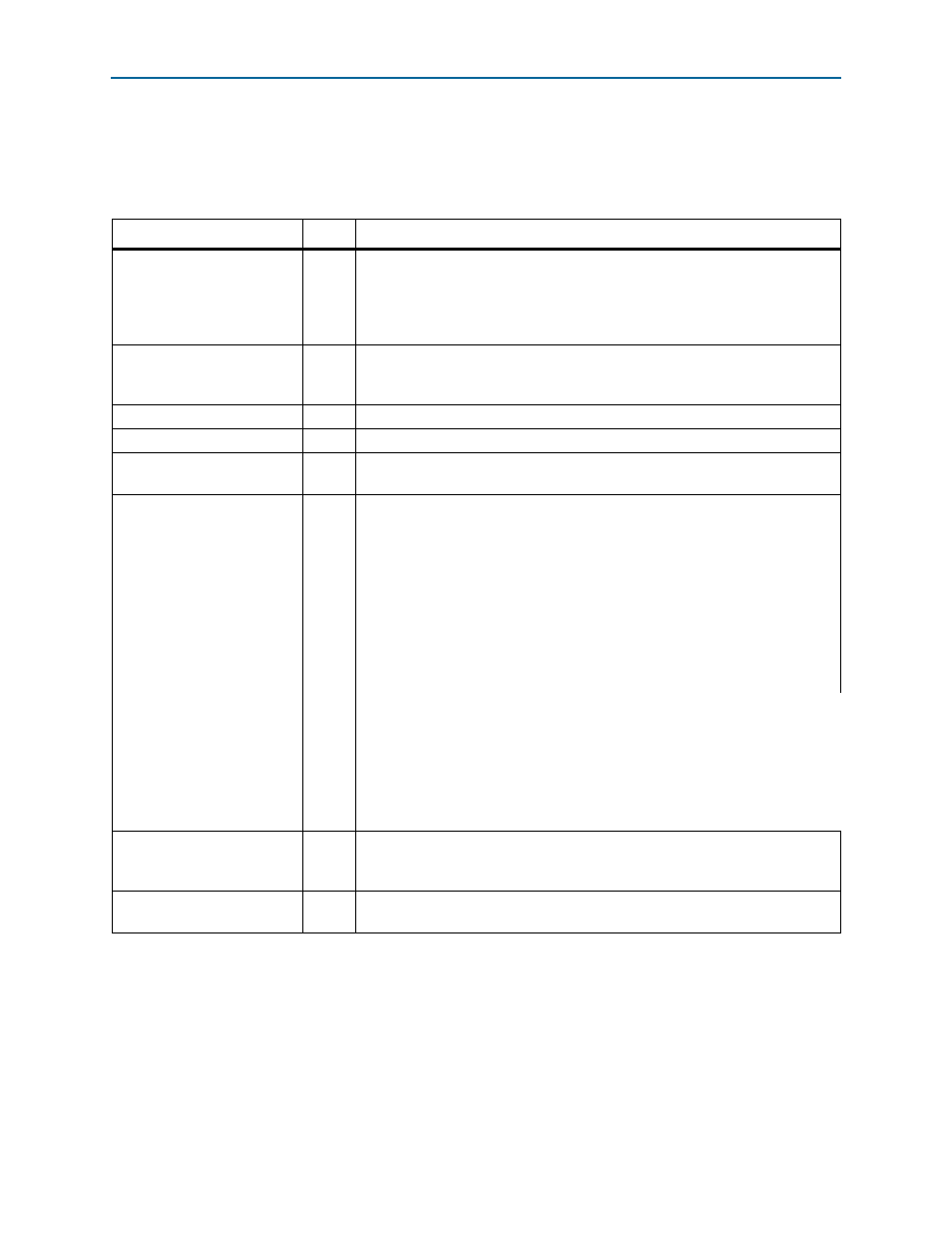

Table 5–20. Avalon-ST Pass-Through Interface Receiver Signals

Signal Type

Function

gen_rx_ready

Input

Indicates to the IP core that the user’s custom logic is ready to receive data on the

next clock cycle. Asserted by the sink to mark ready cycles, which are cycles in

which transfers can occur. If ready is asserted on cycle N, the cycle

(N+READY_LATENCY) is a ready cycle. The RapidIO IP core is designed for

READY_LATENCY

equal to1.

gen_rx_valid

Output

Used to qualify all the other output signals of the receive side pass-through

interface. On every rising edge of the clock where gen_rx_valid is high,

gen_rx_data

can be sampled.

gen_rx_startofpacket

Output

Marks the active cycle containing the start of the packet.

gen_rx_endofpacket

Output

Marks the active cycle containing the end of the packet.

gen_rx_data

Output

A 32-bit wide data bus for 1x mode, or a 64-bit wide data bus for 2x or 4x mode.

gen_rx_empty

Output

This bus identifies the number of empty bytes on the last data transfer of the

gen_rx_endofpacket

. For a 32-bit wide data bus, this bus is 2 bits wide. For a

64-bit wide data bus, this bus is 3 bits wide. The least significant bit is ignored

and assumed to be 0. The following values are supported:

32-bit bus:

2'b0X

none

2'b1X

[15:0]

64-bit bus:

3'b00X

none

3'b01X [15:0]

3'b10X [31:0]

3'b11X [47:0]

If the received number of bytes, including padding and CRC, is a multiple of four

(for a 32-bit wide data bus) or a multiple of eight (for a 64-bit wide data bus), the

value of gen_rx_empty is zero.

The value of gen_rx_empty does not tell you whether the final 16 bits of the data

transfer are padding or CRC bits; your custom logical layer application must

decode the header fields to determine how to interpret the received bits. Refer to

“CRC Checking and Removal” on page 4–12

.

gen_rx_size

Output

Identifies the number of cycles the current packet transfer requires. This signal is

only valid on the start of packet cycle when gen_rx_startofpacket is asserted.

gen_rx_error

Output

Indicates that the corresponding data has an error. This signal is never asserted

by the RapidIO IP core.

Notes to

:

(1) gen_rx_valid is used to qualify all the other output signals of the receive side Avalon-ST pass-through interface.

(2) This is not an Avalon-ST signal. The gen_rx_size signal is exported when the RapidIO IP core is part of a Qsys system.