Altera RapidIO MegaCore Function User Manual

Page 195

Additional Information

Info–3

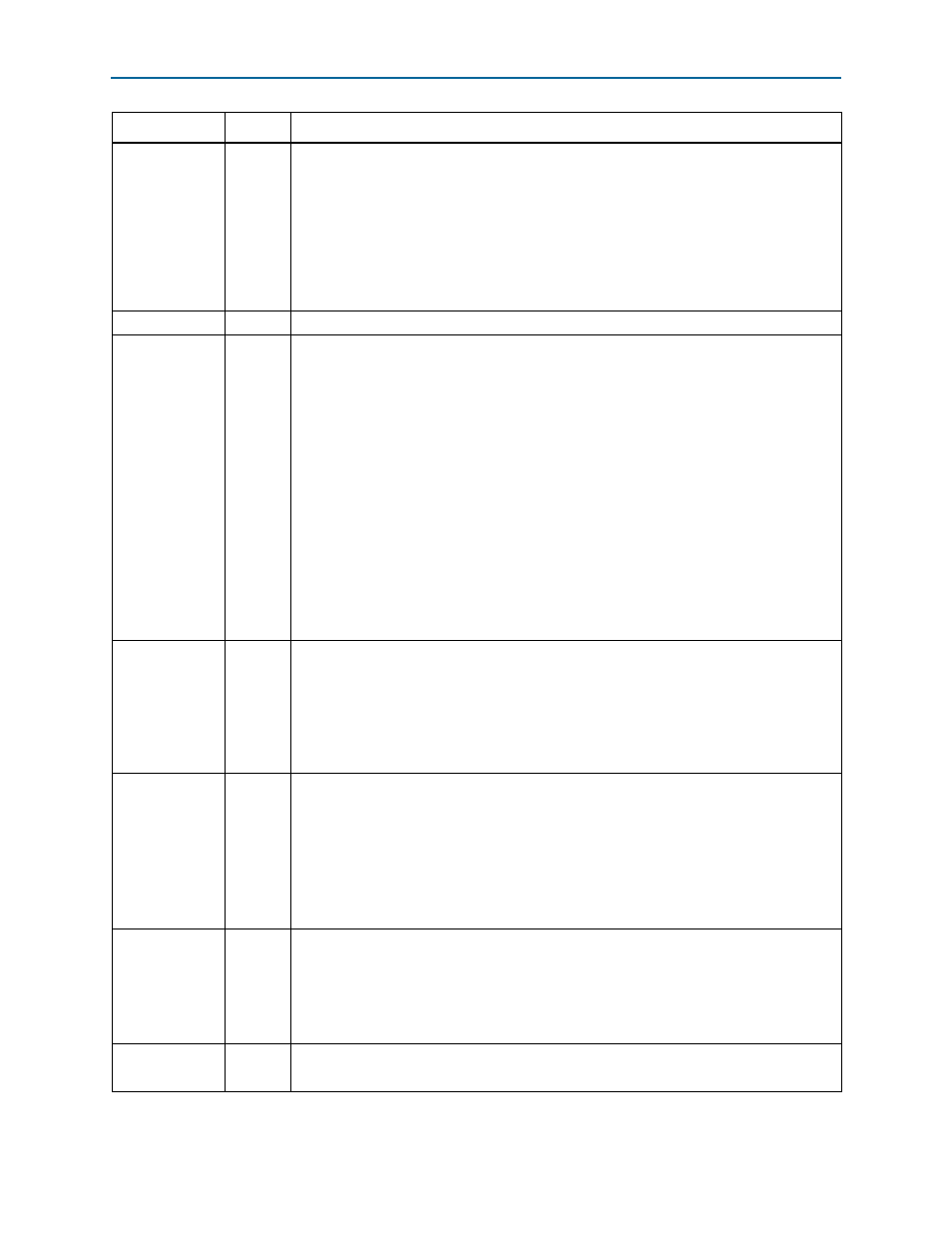

Document Revision History

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

June 2014

(continued)

14.0

■

Updated migration information in

Appendix C, Porting a RapidIO Design from the Previous

and removed information about porting from SOPC Builder.

■

Removed dedicated appendix and other information about the XGMII external transceiver

interfaces. This interface is not available for any of the current supported device families.

■

Removed some information about signals exported by Qsys from

redundant information about Qsys renaming capability. Qsys is documented in the

Quartus II Handbook.

■

Corrected direction of rxgxbclk output clock signal in

“Transceiver Signals” on page 5–4

.

May 2013

13.0

■

Removed SOPC Builder design flow, which is no longer available.

May 2013

13.0

■

Added 2x mode for variations that target any Arria V, Cyclone V, or Stratix V device,

including modification of the descriptions of the PORT_WIDTH and INIT_WIDTH fields in

Port 0 Control

CSR in

to include 2x mode options. This feature is available

in the Quartus II software 13.0 release and later.

■

Added support for Arria V GZ, Arria V SX, Arria V ST, Cyclone V SX, and Cyclone V ST

devices. This support is available in the Quartus II software 12.1 release and later.

■

Updated resource utilization information for Arria V, Cyclone V, and Stratix V devices.

■

Updated Cyclone V GT and Stratix V speed grade support information in

Table 1–7

. Split

device speed grade table

Table 1–7

information into two tables,

,

Device Family Speed Grades for Newer Devices (1)

Family Speed Grades for Legacy Devices (1)

■

Corrected entries in

,

Write Request Size Encoding (32-bit datapath)

,

Read Request Size Encoding (64-bit datapath)

.

■

Corrected and enhanced information about gen_rx_empty output signal in

,

Avalon-ST Pass-Through Interface Receiver Signals

May 2012

12.0

■

Added support for Cyclone V GT ×1 variation at 5.0 Gbaud.

■

Updated speed grade support for Arria V, Stratix IV GX, and Stratix V devices.

■

Moved Modular Configurations section from

Chapter 1, About This MegaCore Function

to

new

Appendix D, Calculating Resource Utilization for Modular Configurations

.

■

Clarified additional constraints on deassertion of reset_n and phy_mgmt_clk_reset in

“Clocking and Reset Structure” on page 4–3

and in

Chapter 5, Signals

.

November 2011

11.1

■

Added support for Arria V and Cyclone V devices. Variations that target one of these two

device families configure the transceiver with the Custom PHY IP core.

■

Added

Chapter 9, Qsys Design Example

.

■

Enhanced description of arxmty signal in

Table 5–7 on page 5–4

.

■

Updated simulation sections in

Chapter 2, Getting Started

.

■

Refered to new

page for information about IP core support level

for many device families.

May 2011

11.0

■

Upgraded to final support for Arria II GZ, Cyclone III LS, and Cyclone IV GX devices.

■

Upgraded to HardCopy Compilation support for HardCopy III, HardCopy IV E, and

HardCopy IV GX devices.

■

Added preliminary support for Stratix V devices.

■

Added support for Custom PHY IP core in variations that target a Stratix V device.

December 2010

10.1

■

Added beta support for Qsys system integration tool.

■

Added read-only version of Port 0 Local AckID CSR.

Date

Version

Changes