Table 4–12 – Altera RapidIO MegaCore Function User Manual

Page 95

Chapter 4: Functional Description

4–49

Logical Layer Modules

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

lists the allowed burst count, byteenable, and address bit 2 value

combinations for RapidIO IP core variations with a 32-bit Avalon-MM interface.

Avalon-MM value combinations not listed in

flag interrupts in the RapidIO

IP core. For more information about the relevant interrupts, refer to

41–48

0

1

1110

49–56

0

0

1111

57–64

0

1

1111

Notes to

(1) For read transfers, the read size of the request packet is rounded up to the next supported size, but only the number

of words corresponding to the requested read burst size is returned.

(2) Burst transfers of more than one Avalon-MM word must start on a double-word aligned Avalon-MM address. If

the slave read burst count is larger than one and io_s_rd_address[0] is not zero, the transfer completes in the

same manner as a failed mapping: the READ_OUT_OF_BOUNDS bit in the Input/Output Slave Interrupt

register is set, sys_mnt_s_irq is asserted if enabled, and the transfer is marked as errored by asserting

io_s_rd_readerror

for the duration of the burst.

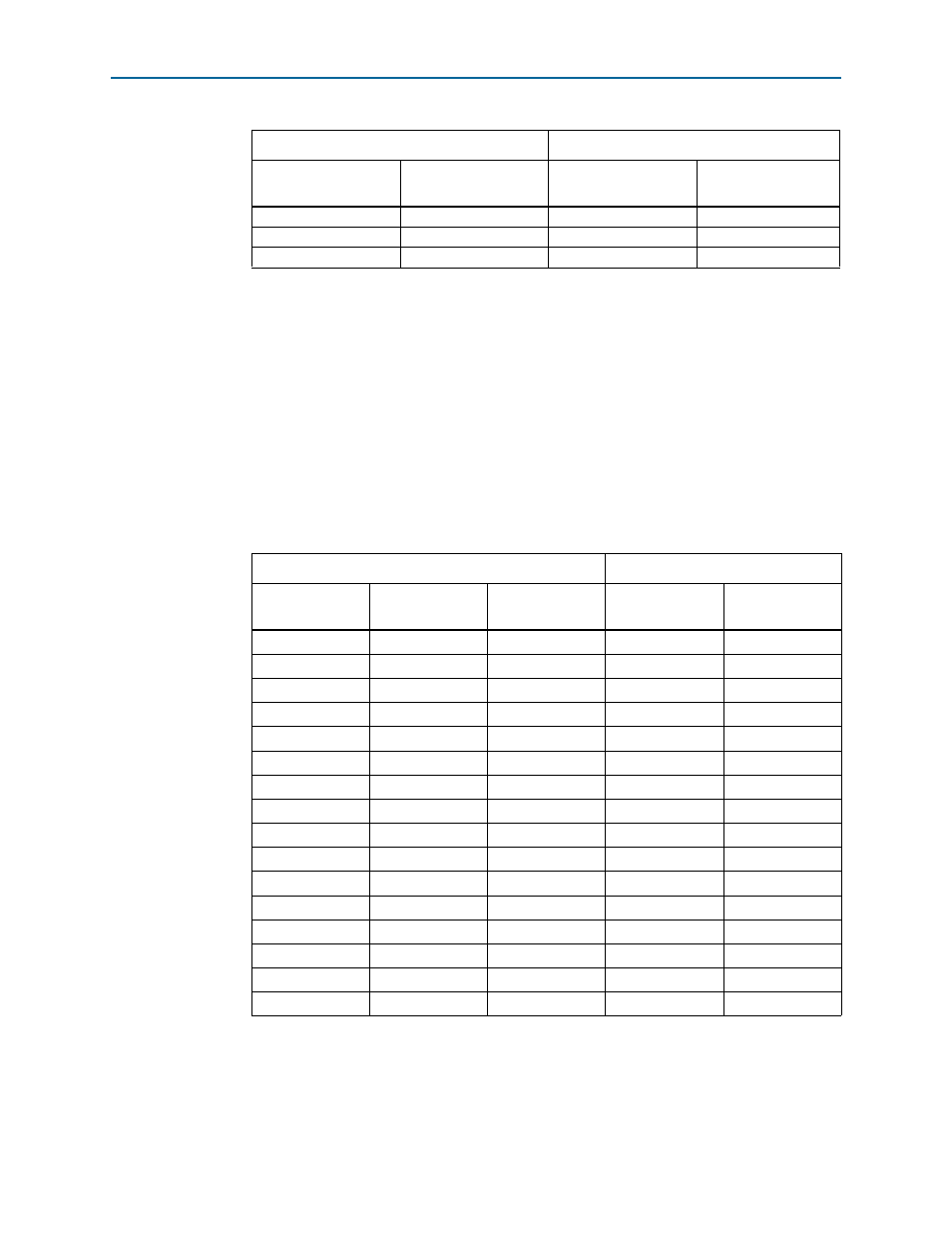

Table 4–12. Write Request Size Encoding (32-bit datapath) (Part 1 of 2)

Avalon-MM Values

RapidIO Values

burstcount

byteenable

(4'bxxxx)

(1'bx)

wdptr

(1'bx)

wrsize

(4'bxxxx)

1

1000

1

0

0000

1

0100

1

0

0001

1

0010

1

0

0010

1

0001

1

0

0011

1

1000

0

1

0000

1

0100

0

1

0001

1

0010

0

1

0010

1

0001

0

1

0011

1

1100

1

0

0100

1

1

0

0101

1

0011

1

0

0110

1

1100

0

1

0100

1

0

1

0101

1

0011

0

1

0110

1

1111

1

0

1000

1

1111

0

1

1000

Table 4–11. Read Request Size Encoding (32-bit datapath) (Part 2 of 2)

Avalon-MM Values

RapidIO Values

burstcount

(1)

address[0]

(2)

(1'bx)

wdptr

(1'bx)

rdsize

(2)

(4'bxxxx)