Altera RapidIO MegaCore Function User Manual

Page 105

Chapter 4: Functional Description

4–59

Logical Layer Modules

August 2014

Altera Corporation

RapidIO MegaCore Function

User Guide

Bits [31:0] of the gen_rx_data bus are ignored in cycle 5 as the gen_rx_empty signals

indicates that 4 bytes are not used in the end-of-packet word. In the case of a

RapidIO IP core variation with 16-bit device ID, the value of gen_rx_empty would be

2

, and only bits [15:0] of the gen_rx_data bus would be ignored in cycle 5.

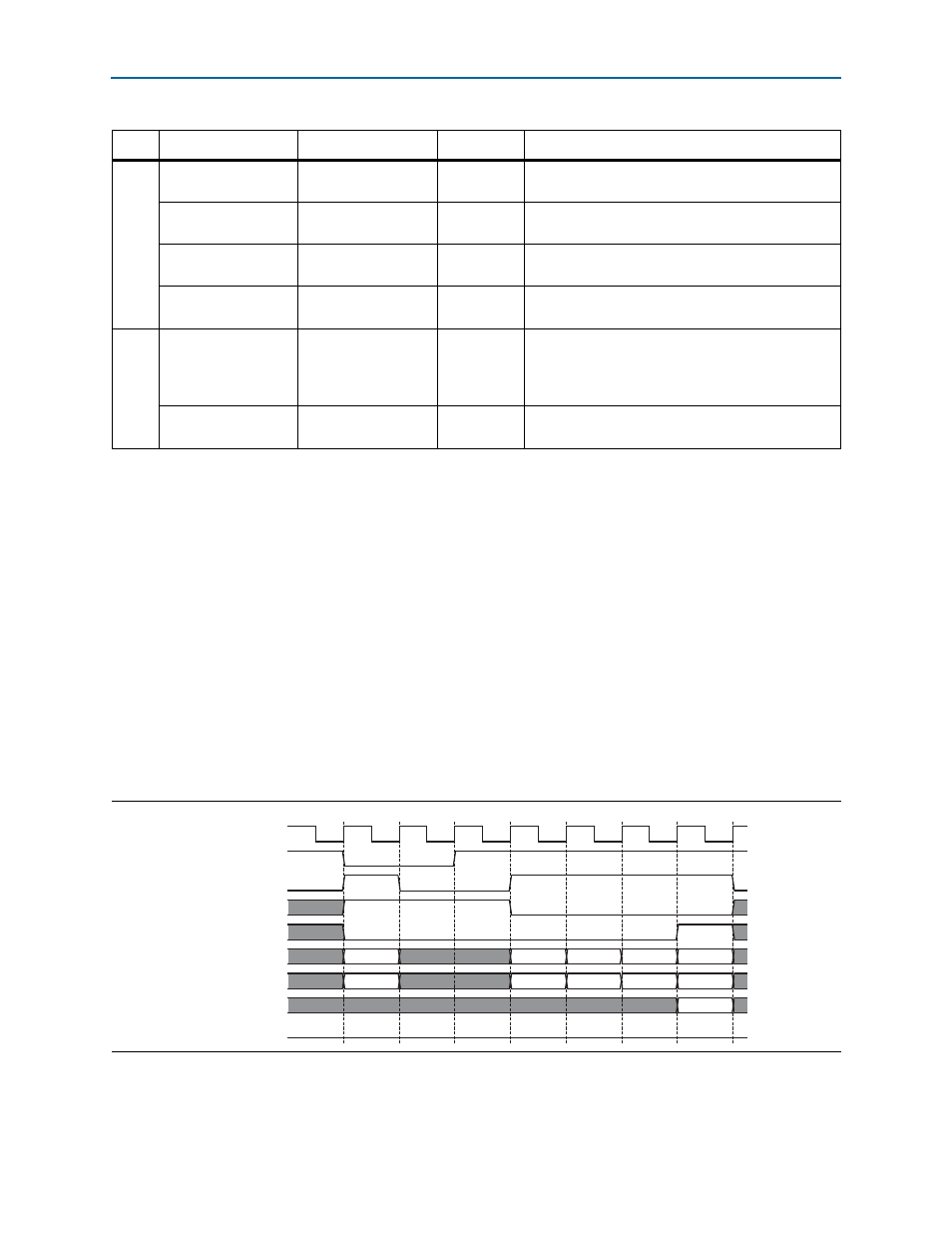

NREAD Example Using Tx Port on Avalon-ST Pass-Through Interface

The next example shows the response to an NREAD transaction in a RapidIO IP core

variation with 16-bit device ID. The response is presented on the Tx port of the

Avalon-ST pass-through interface. The transaction diagram in

shows the

packet presented on this interface. The values captured on a rising clock edge are

those shown in the previous clock cycle, because values change after the rising clock

edge.

4

Payload

Byte14,15

[63:48]

16'h0e0f

Payload

Byte16,17

[47:32]

16'h1011

Payload

Byte18,19

[31:16]

16'h1213

Payload

Byte20,21

[15:0]

16'h1415

5

CRC[15:0]

[63:48]

16'hd37c

For packets with a

payload

greater than 80 bytes,

the first

CRC

field is removed but the final

CRC

field

is not removed. For packets smaller than 80 bytes,

the

CRC

field is not removed.

Pad bytes

[47:32]

16'h0000

The RapidIO requires that Pad bytes be added for

the

payload

to adhere to 32-bit alignment.

Note to

:

(1) In the case of a RapidIO IP core variation with 16-bit device ID, the destinationID and sourceID fields expand to a width of 16 bits each, and the

fields described in the table rows following the destinationID field are shifted to the right and to the following clock cycles.

Table 4–15. RapidIO Header Fields and gen_rx_data Bus Payload (Part 2 of 2)

Cycle

Field

gen_rx_data bus

Value

Comment

Figure 4–31. Packet Transmitted on the Avalon ST Pass-Through Interface

gen_tx_ready

system clock

gen_tx_valid

gen_tx_startofpacket

gen_tx_endofpacket

gen_tx_data[63:32]

gen_tx_data[31:0]

gen_tx_empty[2:0]

gen_tx_error

209DCCDC

01020304

090A0B0C

11121314

191A1B1C

AABA8000

05060708

0D0E0F10

15161718

1D1E1F20

0

0

1

2

3

4

5

6

7

READY_LATENCY

= 1

READY_LATENCY

= 1

ready cycle

ready cycle

ready cycle

ready cycle ready cycle ready cycle