Heading1 - dffns, Figure - figure 2-13: logic symbol, Heading2 - pins – Achronix Speedster22i User Macro Guide User Manual

Page 93: Table - table 2-42: pin descriptions, Heading2 - parameters, Table - table 2-43: parameters, Heading3 - init, Heading3 - sr_assertion, Dffns, Pins

Registers

DFFNS

Speedster22i Macro Cell Library

PAGE 77

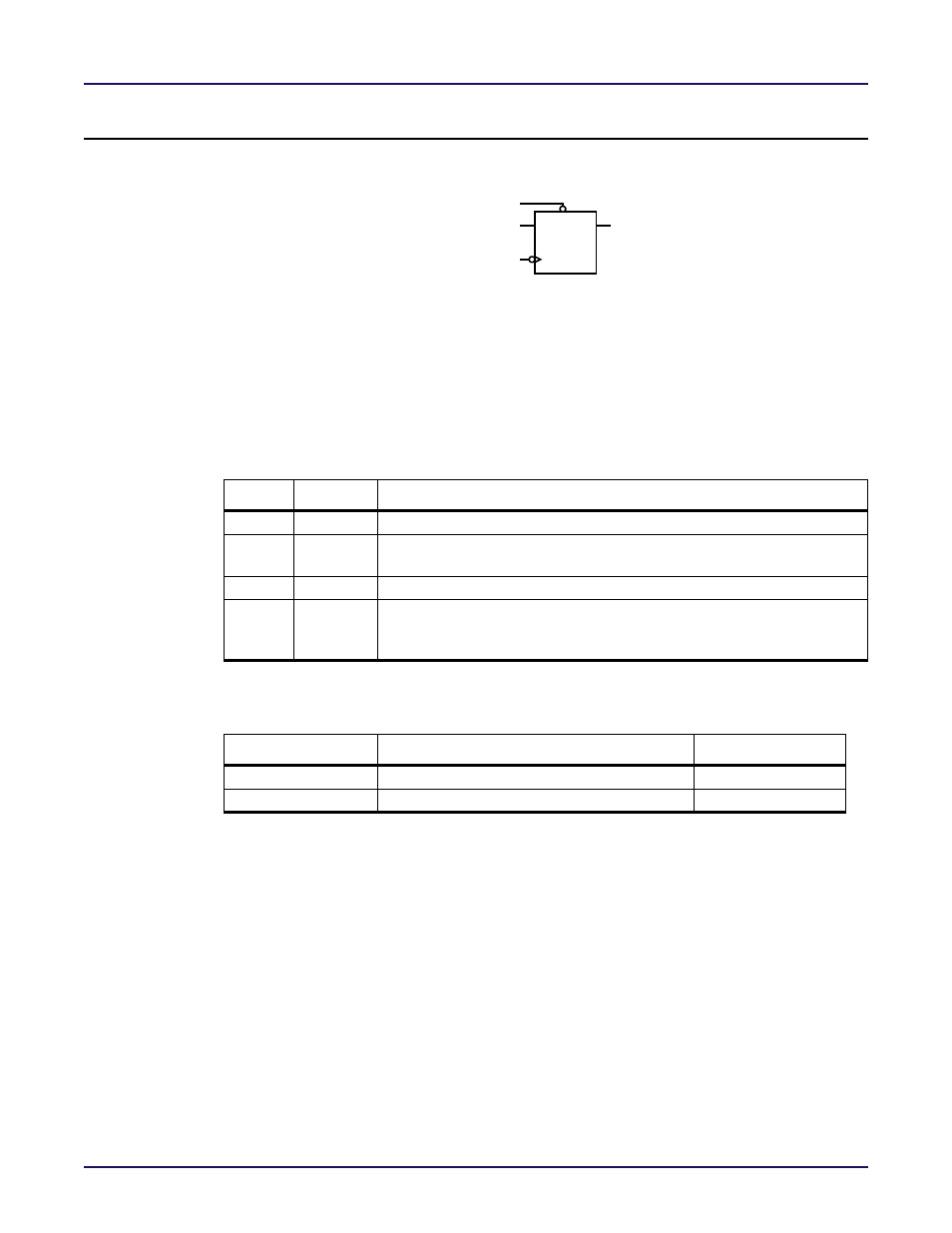

DFFNS

Negative Clock Edge D-Type Register with Asynchronous Set

sn

d

ckn

DFFNS

q

Figure 2-13: Logic Symbol

DFFNS is a single D‐type register with data input (d), clock (ckn), and active‐low set (sn)

inputs and data (q) output. The active‐low set input overrides all other inputs when it is

asserted low and sets the data output high. If the asynchronous set input is not asserted, the

data output is set to the value on the data input upon the next falling edge of the clock.

Pins

Table 2-42: Pin Descriptions

Name

Type

Description

d

Data input.

sn

Active-low asynchronous set input. A low on sn sets the q output high

independent of the other inputs.

ckn

Negative-edge clock input.

q

Data output. The value present on the data input is transferred to the q

output upon the falling edge of the clock if the asynchronous set input is

high.

Parameters

Table 2-43: Parameters

Parameter

Defined Values

Default Value

init

1’b1

sr_assertion

“unclocked”

init

The init parameter defines the initial value of the output of the DFFNS register. This is the

value the register takes upon the initial application of power to the FPGA. The default value

of the init parameter is 1’b1.

sr_assertion

The sr_assertion parameter defines the behavior of the output when the sn set input is

asserted. Assigning the sr_assertion to “unclocked” results in an asychronous assertion of the

reset signal, where the q output is set to one upon assertion of the active‐low reset signal.

Assigning the sr_assertion to “clocked” results in a synchronous assertion of the reset signal,

where the q output is set to one at the next rising edge of the clock. The default value of the

sr_assertion parameter is “unclocked”.

input

input

input

output

1’b0, 1’b1

“unclocked”, “clocked”