Heading3 - write error flag, Heading3 - read error flag – Achronix Speedster22i User Macro Guide User Manual

Page 183

Memories

LRAMFIFO

Speedster22i Macro Cell Library

PAGE 166

of blind writes to the FIFO that can be made without monitoring the full flag. For example, if

the afull_offset parameter is set to 7’h04 and the almost_full flag is deasserted, the user is

guaranteed that there are at least five empty locations in the FIFO. The user may write all five

words without monitoring the full flag and be guaranteed that these words will be written to

the FIFO and the write_err flag will not be asserted. The Almost Full flag is synchronous with

the wrclk clock input.

Write Error Flag

The Write Error (write_err) flag is asserted in the following wrclk clock cycle when the user

tries to write the FIFO while the Full Flag is high.

Read Error Flag

The Read Error (read_err) flag is asserted in the following rdclk clock cycle when the user tries

to read the FIFO while the Empty Flag is high.

Flag Latency in Asynchronous Mode (ptr_sync_mode = 1’b0)

The empty, full, almost_empty, and almost_full flags are calculated based on comparisons

between the FIFO write pointer and the FIFO read pointer. The write pointer is synchronous

to the wrclk domain and the read pointer is synchronous to the rdclk domain.

For the case of an asynchronous FIFO, the wrclk and rdclk clocks reside in different clock

domains.

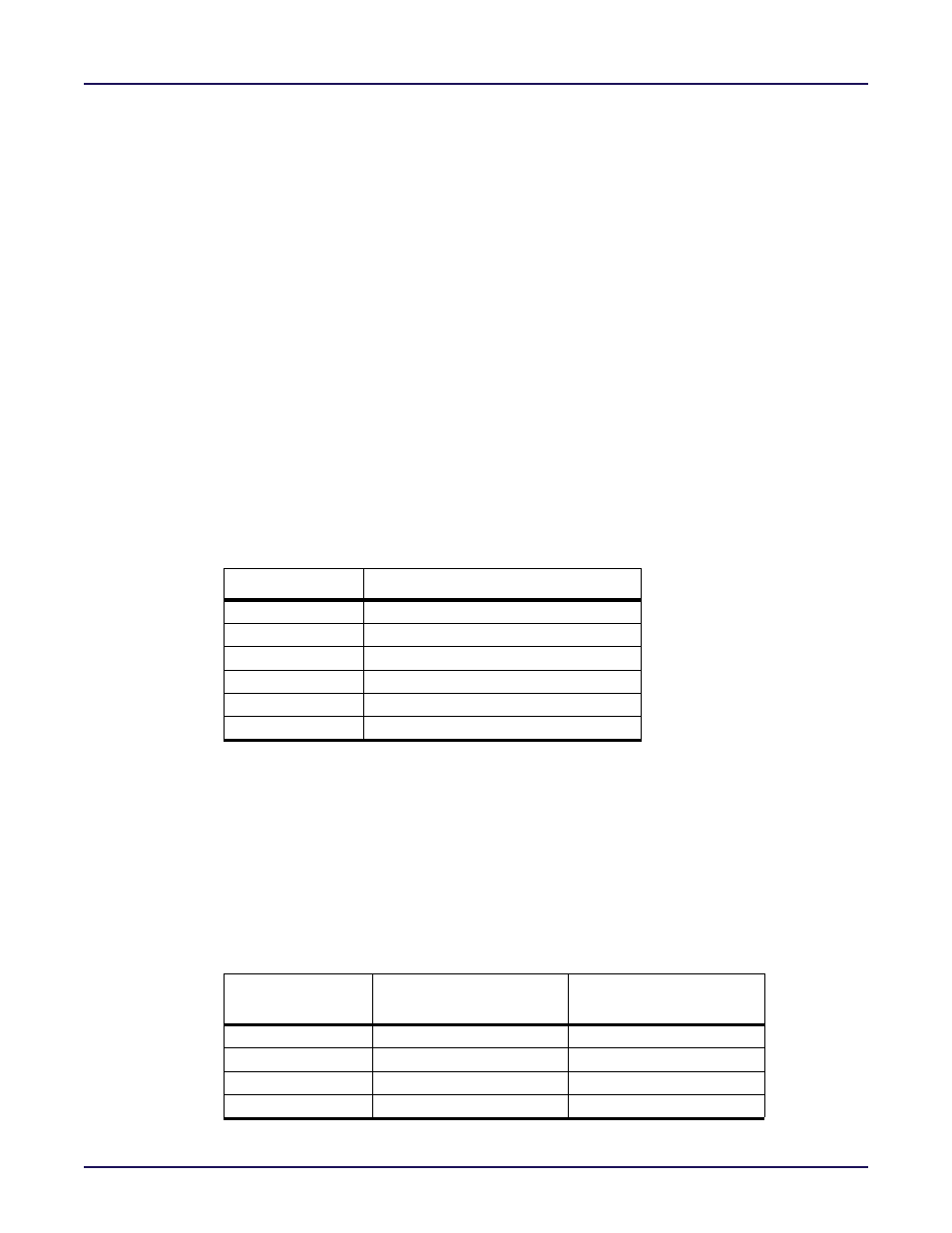

Table 6-58: FIFO Pointers and Status Flag Clock Domain Assignments

Flag

Associated Clock Domain

FIFO Write Pointer

wrclk

FIFO Read Pointer

rdclk

empty flag

rdclk

almost_empty flag

rdclk

full flag

wrclk

almost_full flag

wrclk

Before flag calculations can be made, circuitry has to make sure that both pointers are in the

same clock domain as the flag for which the calculation is done. The Write Pointer

Synchronizer

Figure 6‐33: Write Pointer Synchronizer Block Diagram

Synchronizer

Figure 6‐34: Read Pointer Synchronizer Block Diagram

are used to transfer

each of the pointers into the other clock domain. In order to synchronize a given pointer to the

opposite clock domain, a series of registers, whose depth is determined by the

wrptr_sync_stages and rdptr_sync_stages parameters, is used. The transfer of a pointer

through these registers adds additional delay to the flag calculation. The versions of the

pointers used for flag calculations are shown below in

Table 6‐59: Pointers Used for FIFO

Flag Calculations (ptr_sync_mode = 1’b0)

.

Table 6-59: Pointers Used for FIFO Flag Calculations (ptr_sync_mode = 1’b0)

Flag

Write Pointer Used for

Flag Calculation

Read Pointer Used for

Flag Calculation

empty flag

Synchronized Write Pointer

Read Pointer

almost_empty flag

Synchronized Write Pointer

Read Pointer

full flag

Write Pointer

Synchronized Read Pointer

almost_full flag

Write Pointer

Synchronized Read Pointer