Heading3 - sr_assertion, Heading3 - verilog instantiation template, Table – Achronix Speedster22i User Macro Guide User Manual

Page 77: Table 2‐20: dffes, Function table when sr_assertion = “clocked

Registers

DFFES

Speedster22i Macro Cell Library

PAGE 61

sr_assertion

The sr_assertion parameter defines the behavior of the output when the sn set input is

asserted. Assigning the sr_assertion to “unclocked” results in an asychronous assertion of the

reset signal, where the q output is set to one upon assertion of the active‐low reset signal.

Assigning the sr_assertion to “clocked” results in a synchronous assertion of the reset signal,

where the q output is set to one at the next rising edge of the clock. The default value of the

sr_assertion parameter is “unclocked”.

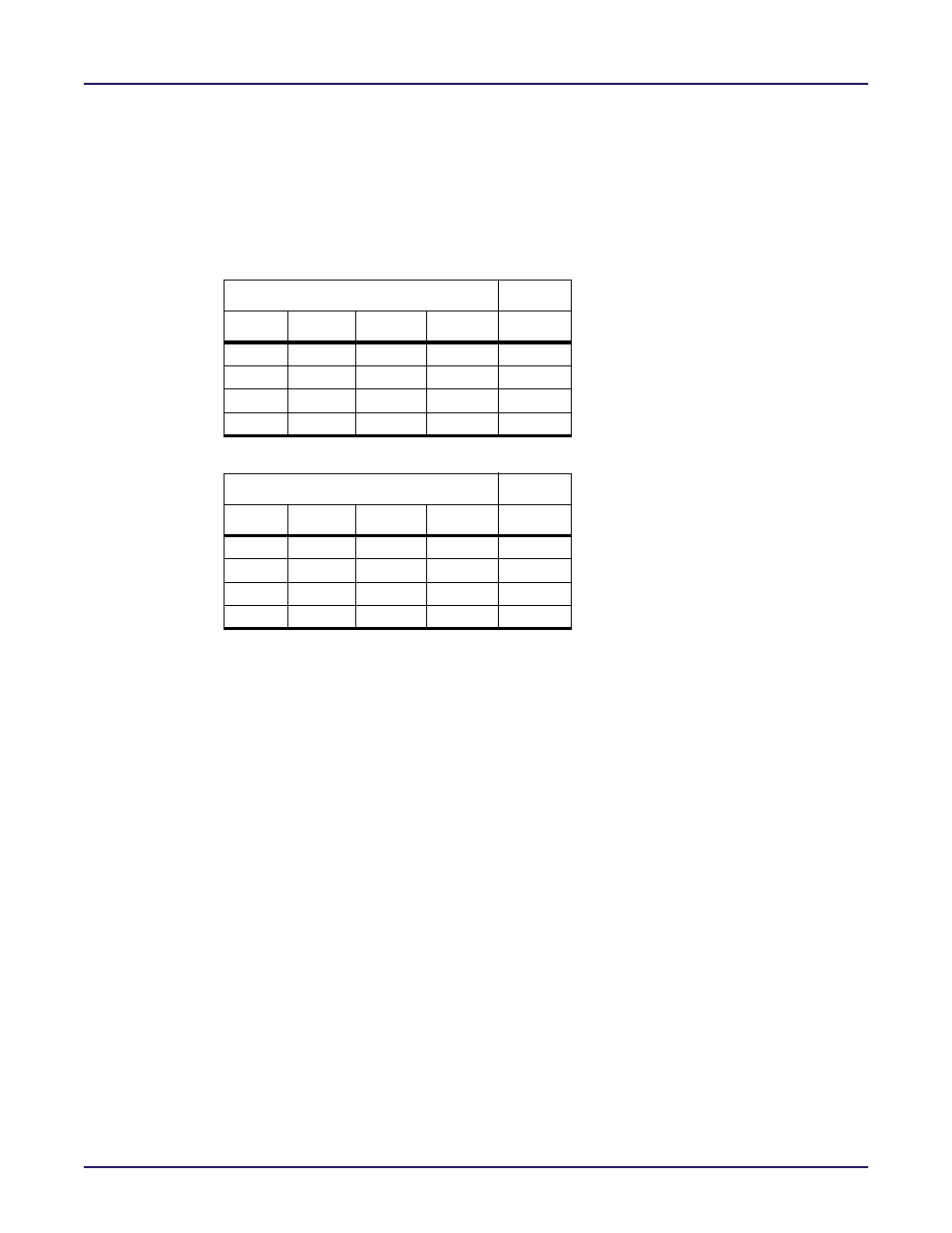

Table 2-19: DFFES Function Table when sr_assertion = “unclocked”

Inputs

Output

sn

ce

d

ck

q

Table 2-20: DFFES Function Table when sr_assertion = “clocked”

Inputs

Output

sn

ce

d

ck

q

Verilog Instantiation Template

DFFES #(.init(1’b1),

.sr_assertion(“unclocked”))

instance_name

(.q(user_out),

.d(user_din),

.sn(user_set),

.ce(user_clock_enable),

.ck(user_clock));

0

X

X

X

1

1

0

X

X

Hold

1

1

0

0

1

1

1

1

0

X

X

1

1

0

X

X

Hold

1

1

0

0

1

1

1

1