Writing and reading a mixed-width fifo, Limitations of concurrent read/write operations – Achronix Speedster22i User Macro Guide User Manual

Page 163

Memories

BRAM80KFIFO

Speedster22i Macro Cell Library

PAGE 146

Writing and Reading a Mixed-Width FIFO

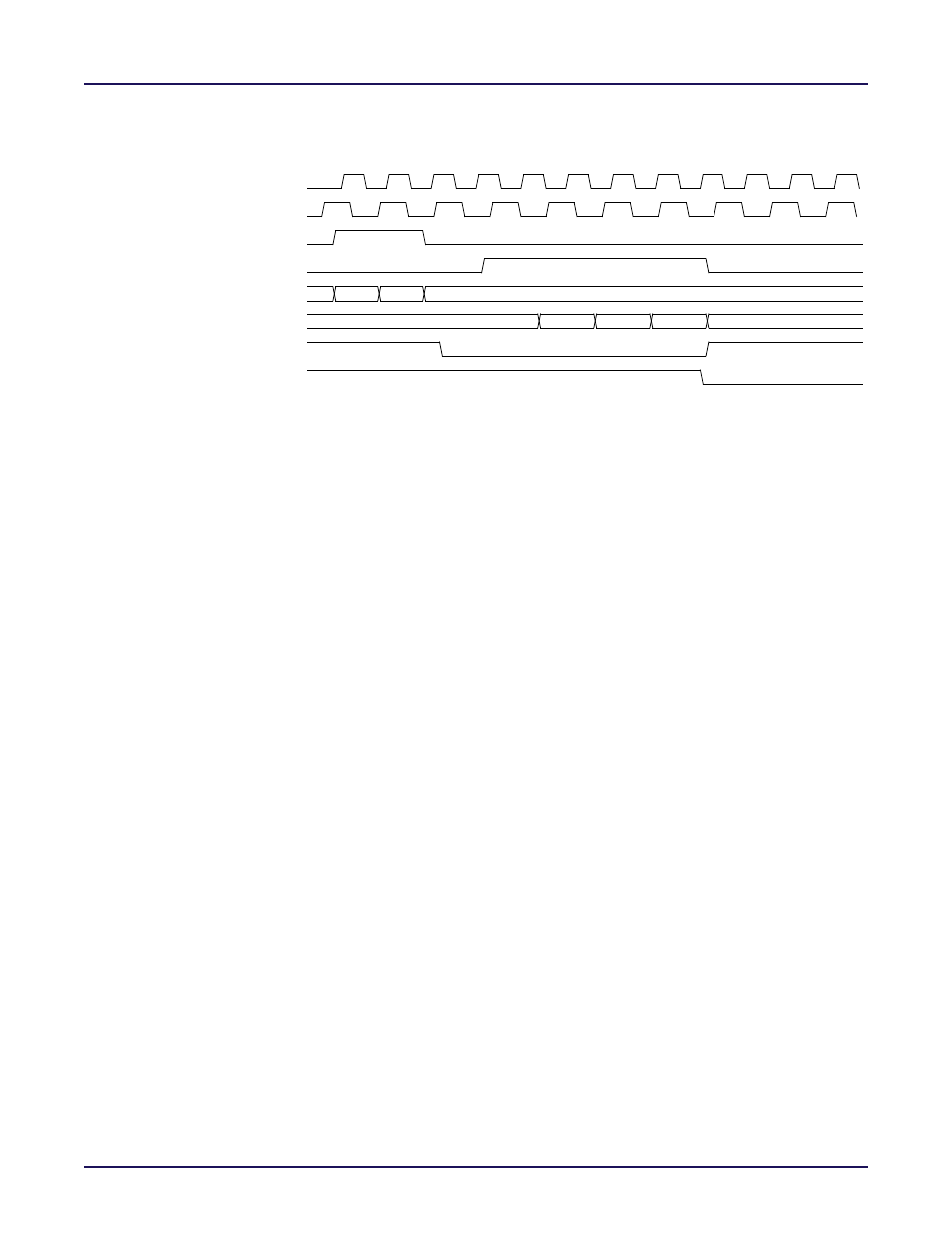

Figure 6-21: Writing and Reading a Mixed-Width FIFO

Limitations of Concurrent Read/Write Operations

FIFO operations may be performed simultaneously from both sides of the memory, however

there is a restriction with memory collisions. A memory collision is defined as the condition

where both of the ports access the same memory address within the same clock cycle (both

ports connected to the same clock), or within a TBD ps window (if each port is connected to a

different clock). If one of the ports is writing an address while the other port is reading the

same address, the write operation will occur, but the read data will be invalid. If the user

programs either the en_wr_when_full or en_rd_when_empty parameters to 1’b1, it is possible

for simultaneous memory operations to occur, resulting in corrupted reads from the FIFO.

Even though memory collisions corrupt the read data, no damage to the hardware will occur.

wrclk

rdclk

wren

rden

din

dout

empty

almost_empty

2. wptr_sync_stages = 2’b00

Note: This timing diagram assumes:

3. sync_mode = 1’b0

4. fwft = 1’b0

word 0

word 0[15:0]

word 1

word 0[31:16] word 1[15:0] word 1[31:16]

1. write_width = 32, read_width = 16