Achronix Speedster22i User Macro Guide User Manual

Page 113

Memories

BRAM80K

Speedster22i Macro Cell Library

PAGE 96

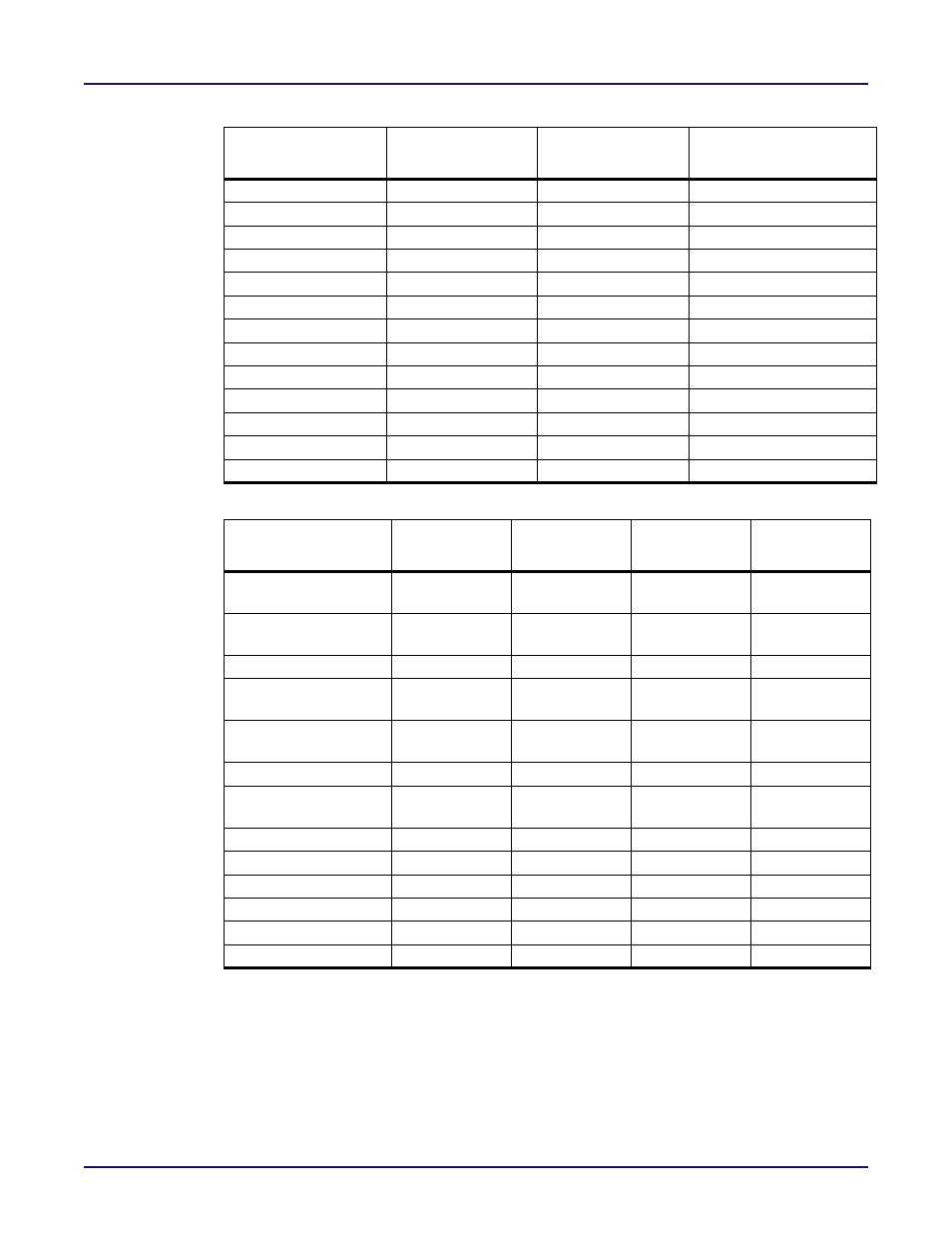

Table 6-8: dina(dinb) bit assignments per porta_write_width(portb_write_width) values

porta_write_width,

portb_write_width

dinpxa[3:0],

dinpxb[3:0]

dinpa[3:0],

dinpb[3:0]

dina[31:0], dinb[31:0]

user_din[39:36]

user_din[35:32]

user_din[31:0]

4’hx

user_din[35:32]

user_din[31:0]

4’hx

4’hx

user_din[31:0]

2’bxx,user_din[19:18] 2’bxx,user_din[17:16]

16’hxxxx,user_din[15:0]

4’hx

user_din[17:16]

16’hxxxx,user_din[15:0]

4’hx

4’hx

16’hxxxx,user_din[15:0]

3’bxxx,user_din[9]

3’bxxx,user_din[8]

24’hxxxxxx,user_din[7:0]

4’hx

3’bxxx,user_din[8]

24’hxxxxxx,user_din[7:0]

4’hx

4’hx

24’hxxxxxx,user_din[7:0]

4’hx

3’bxxx,user_din[4]

28’hxxxxxxx,user_din[3:0]

4’hx

4’hx

28’hxxxxxxx,user_din[3:0]

4’hx

4’hx

30’hxxxxxxxx,user_din[1:0]

4’hx

4’hx

31’hxxxxxxxx,user_din[0]

Table 6-9: Write Enable to Data Input Bus Mapping per Write Port Width

porta_write_width

(portb_write_width)

wea[3]

(web[3])

wea[2]

(web[2])

wea[1]

(web[1])

wea[0]

(web[0])

dinpx[3],dinp[3],

din[31:24]

dinpx[2],dinp[2],

din[23:16]

dinpx[1],dinp[1],

din[15:8]

dinpx[0],dinp[0],

din[7:0]

dinp[3],

din[31:24]

dinp[2],

din[23:16]

dinp[1],

din[15:8]

dinp[0], din[7:0]

din[31:24]

din[23:16]

din[15:8]

din[7:0]

dinpx[1],dinp[1],

din[15:8]

dinpx[0],dinp[0],

din[7:0]

dinpx[1],dinp[1],

din[15:8]

dinpx[0],dinp[0],

din[7:0]

dinp[1],

din[15:8]

dinp[0], din[7:0]

dinp[1],

din[15:8]

dinp[0], din[7:0]

din[15:8]

din[7:0]

din[15:8]

din[7:0]

dinpx[0],dinp[0],

din[7:0]

dinpx[0],dinp[0],

din[7:0]

dinpx[0],dinp[0],

din[7:0]

dinpx[0],dinp[0],

din[7:0]

dinp[0], din[7:0]

dinp[0], din[7:0]

dinp[0], din[7:0]

dinp[0], din[7:0]

din[7:0]

din[7:0]

din[7:0]

din[7:0]

dinp[0], din[3:0]

dinp[0], din[3:0]

dinp[0], din[3:0]

dinp[0], din[3:0]

din[3:0]

din[3:0]

din[3:0]

din[3:0]

din[1:0]

din[1:0]

din[1:0]

din[1:0]

din[0]

din[0]

din[0]

din[0]

40

36

32

20

18

16

10

9

8

5

4

2

1

40

36

32

20

18

16

10

9

8

5

4

2

1