Heading3 - rdrst_sync_stages, Heading3 - afull_offset, Figure 6‐35: write pointer reset input – Achronix Speedster22i User Macro Guide User Manual

Page 181: Selection block diagram, Rdrst_sync_stages, Afull_offset

Memories

LRAMFIFO

Speedster22i Macro Cell Library

PAGE 164

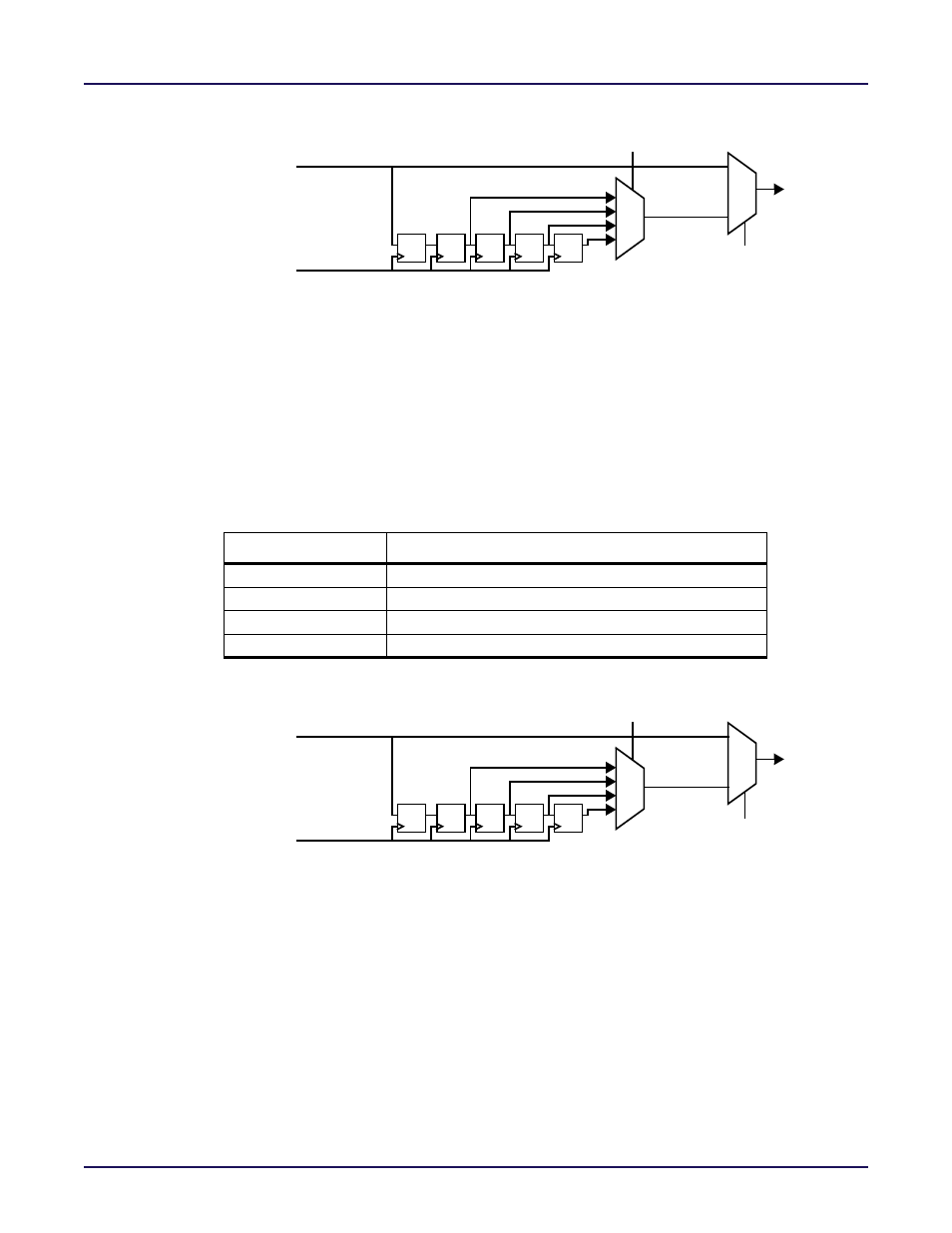

Figure 6-35: Write Pointer Reset Input Selection Block Diagram

rdrst_sync_stages

The rdrst_sync_stages parameter defines the number of stages of registers used to

synchronize the rstn input pin to the wrclk clock domain. The value of the rdrst_sync_stages

parameter is only used if the rst_sync_mode is set to 1’b0. The mapping of the

rdrst_sync_stages parameter value to the number of sychronization stages is defined in

6‐55: Mapping rdrst_sync_stages Parameter Settings to Synchronization Stage Depth

where each stage corresponds to a register in the Read Reset Synchronizer shown in

6‐36: Read Pointer Reset Input Selection Block Diagram

. For example, setting

rdrst_sync_stages to 2’b00 configures the rstn synchronization circuit to have two back‐to‐

back registers in the Write Reset Synchronizer. The default value of the rdrst_sync_stages

parameter is 2’b00.

Table 6-55: Mapping rdrst_sync_stages Parameter Settings to Synchronization Stage Depth

rdrst_sync_stages

Read Reset Synchronization Stage Depth

2’b00

2

2’b01

3

2’b10

4

2’b11

5

Figure 6-36: Read Pointer Reset Input Selection Block Diagram

afull_offset

The afull_offset parameter defines the word depth at which the FIFO almost_full signal

changes. The almost_full flag may be used to determine the number of blind writes to the

FIFO that can be made without monitoring the full flag. For example, if the afull_offset

parameter is set to 7’h04 and the almost_full flag is deasserted, the user is guaranteed that

there are at least five empty locations in the FIFO. The user may write all five words without

monitoring the full flag and be guaranteed that these words will be written to the FIFO and

the write_err flag will not be asserted. The default value of the afull_offset parameter is 7’h04,

corresponding to five or fewer available locations remain in the FIFO.

Write Reset Synchronizer

d q

d q

d q

d q

d q

00

01

10

11

1

0

rstn

rdclk

Write

Pointer

Reset

rst_sync_mode

wrrst_sync_stages

Read Reset Synchronizer

d q

d q

d q

d q

d q

00

01

10

11

1

0

rstn

rdclk

Read

Pointer

Reset

rdrst_sync_stages

rst_sync_mode