Heading2 - memory initialization, Support for read‐first (read, Before‐write) memory operations – Achronix Speedster22i User Macro Guide User Manual

Page 118: Memory initialization

Memories

BRAM80K

Speedster22i Macro Cell Library

PAGE 101

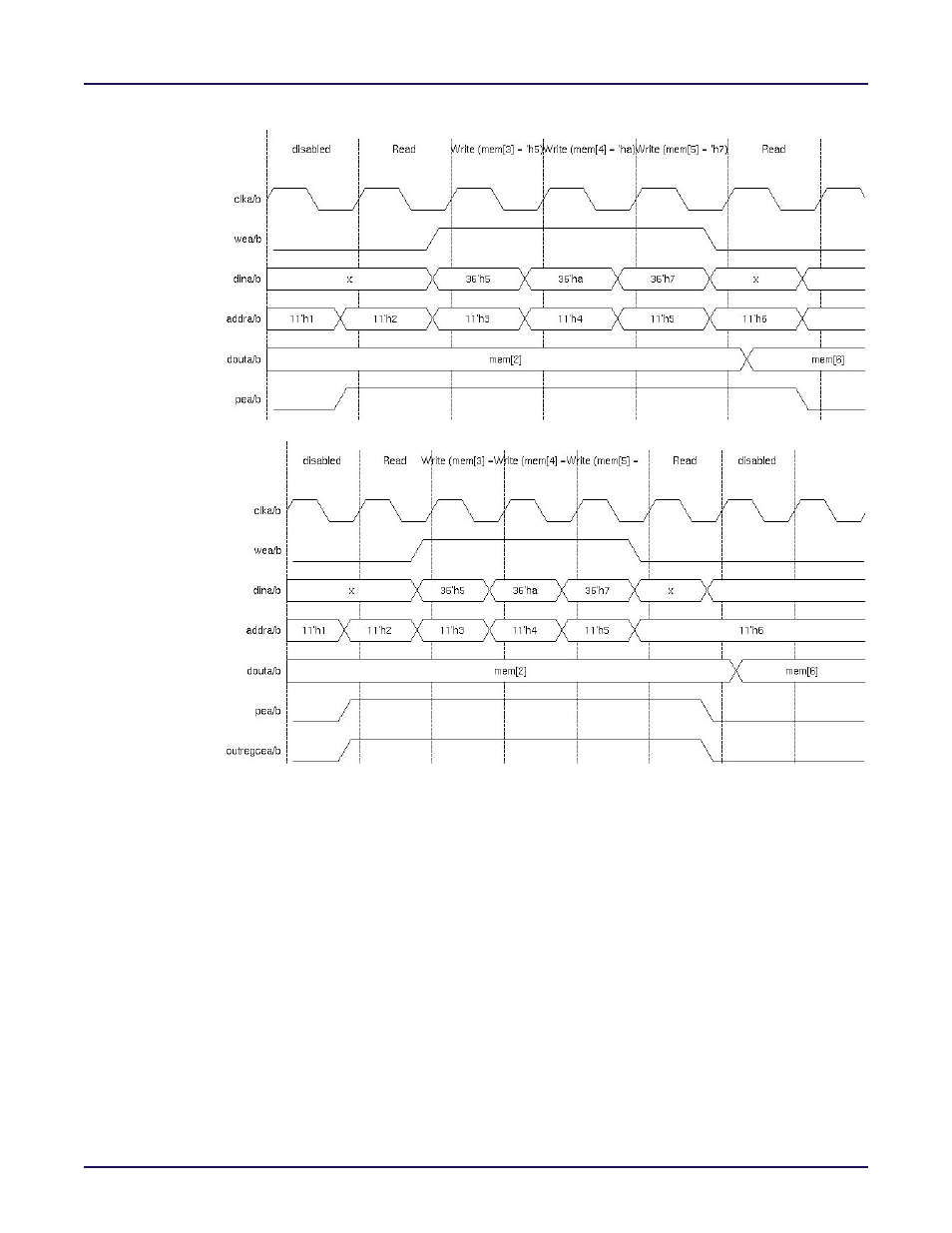

Figure 6-5: No-Change, Latched Mode Timing Diagram

Figure 6-6: No-Change, Registered Mode Timing Diagram

Support for Read-First (Read-Before-Write) Memory Operations

The BRAM80K memory does not directly support read‐first or read‐before‐write mode of

operation. If this behavior is detected by synthesis, a warning will be issued in the synthesis

log file and a register file will be synthesized. To implement a more efficient mapping of a

‘read‐first’ memory, the user should update his code to use an Achronix

BRAM80K_READ_FIRST soft macro. This soft macro block combines a BRAM80K memory

block with LUT circuitry to convert the read‐first memory access into a separate read

operation followed by a write operation at twice the clock rate of the requested clock

frequency. Note that the user will have to provide the BRAM80K_READ_FIRST macro with a

2x clock with one of the on‐chip PLLs.

Memory Initialization

When the BRAM80K memory is configured with port widths of 1, 2, 4, 8, 16, or 32 bits wide,

the initial memory contents may be defined by initializing the 256 256‐bit parameters

initd_000 through initd_255. The data memory is organized as little‐endian with bit 0 mapped

to bit zero of parameter initd_000 and bit 65535 mapped to bit 255 of parameter initd_255.