Heading3 - simultaneous memory operations – Achronix Speedster22i User Macro Guide User Manual

Page 116

Memories

BRAM80K

Speedster22i Macro Cell Library

PAGE 99

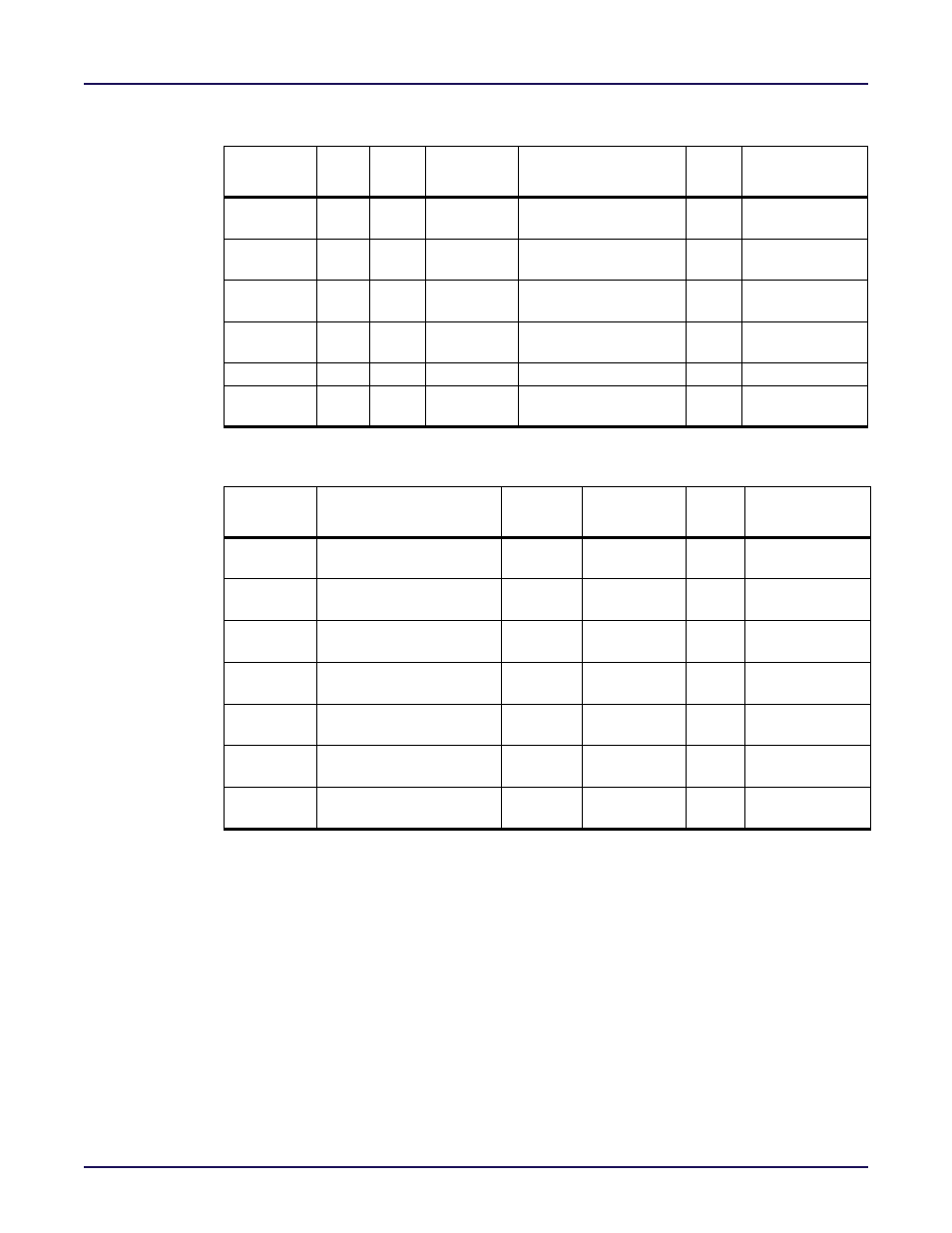

Table 6-13: BRAM Output Function Table for Latched Mode (Assumes active-high clock, port enable,

and latch reset value)

Operation

pea

(peb)

wea

(web)

rstlatcha

(rstlatchb)

porta_write_mode

(portb_write_mode)

clka

(clkb)

douta (doutb)

Table 6-14: BRAM Output Function Table for Registered Mode (Assumes active-high clock, output

register clock enable, and output register reset)

Operation

porta_regce_priority

(portb_regce_priority)

rstrega

(rstregb)

outregcea

(outregceb)

clka

(clkb)

douta (doutb)

Hold

X

X

X

X

Hold

“rstreg”

0

0

Update

Output

“rstreg”

0

1

latcha_output

(latchb_output)

Reset

Output

“rstreg”

1

X

porta_srval

(portb_srval)

Hold

“regce”

X

0

Update

Output

“regce”

0

1

latcha_output

(latchb_output)

Reset

Output

“regce”

1

1

porta_srval

(portb_srval)

Simultaneous Memory Operations

Memory operations may be performed simultaneously from both sides of the memory,

however there is a restriction with memory collisions. A memory collision is defined as the

condition where both of the ports access the same memory address within the same clock

cycle (both ports connected to the same clock), or within a TBD ps window (if each port is

connected to a different clock). Simultaneous read operations to the same address by both

ports is allowed and will produce valid data on each of the ports. If one of the ports is writing

an address while the other port is reading the same address, the write operation will occur,

but the read data will be invalid. The user may reliably read the data the next cycle if there is

no longer a write collision. If both ports write the same address at the same time, the memory

contents for that memory address will become invalid. While simultaneously writing the

same address from both ports will invalidate the data, no damage to the hardware will occur.

Note that for the special case of the BRAM80K having both ports configured for write_first

mode, a write‐write collision will corrupt the memory contents, but the user will see the

Hold

X

X

X

X

X

douta_previous

(doutb_previous)

Hold

0

X

X

X

douta_previous

(doutb_previous)

Reset

Output

1

X

1

X

porta_srval

(portb_srval)

Read

1

0

0

X

mem[addra]

(mem[addrb])

Write

1

1

0

“write-first”

dina (dinb)

Write

1

1

0

“no_change”

douta_previous

(doutb_previous)

douta_previous

(doutb_previous)

douta_previous

(doutb_previous)

douta_previous

(doutb_previous)