Heading1 - iopad_d, Figure - figure 1-2: iopad_d logic symbol, Iopad_d – Achronix Speedster22i User Macro Guide User Manual

Page 21

I/O Cells

IOPAD_D

Speedster Macro Cell Library

PAGE 4

IOPAD_D

Bidirectional Registered I/O Pad with Asynchronous or Synchronous

Set/Reset

q

ce

d

rstn

q

ce

d

rstn

srstn

q

ce

d

rstn

srstn

txrstn

rxrstn

oerstn

din

dout

pad

oe

txclk

rxclk

oeclk

txdata_en

rxdata_en

srstn

Note: For Speedster22iHP, txdata_en and rxdata_en are shared.

For Speedster22iHD, txdata_en and rxdata_en may be driven separately.

IOPAD_D

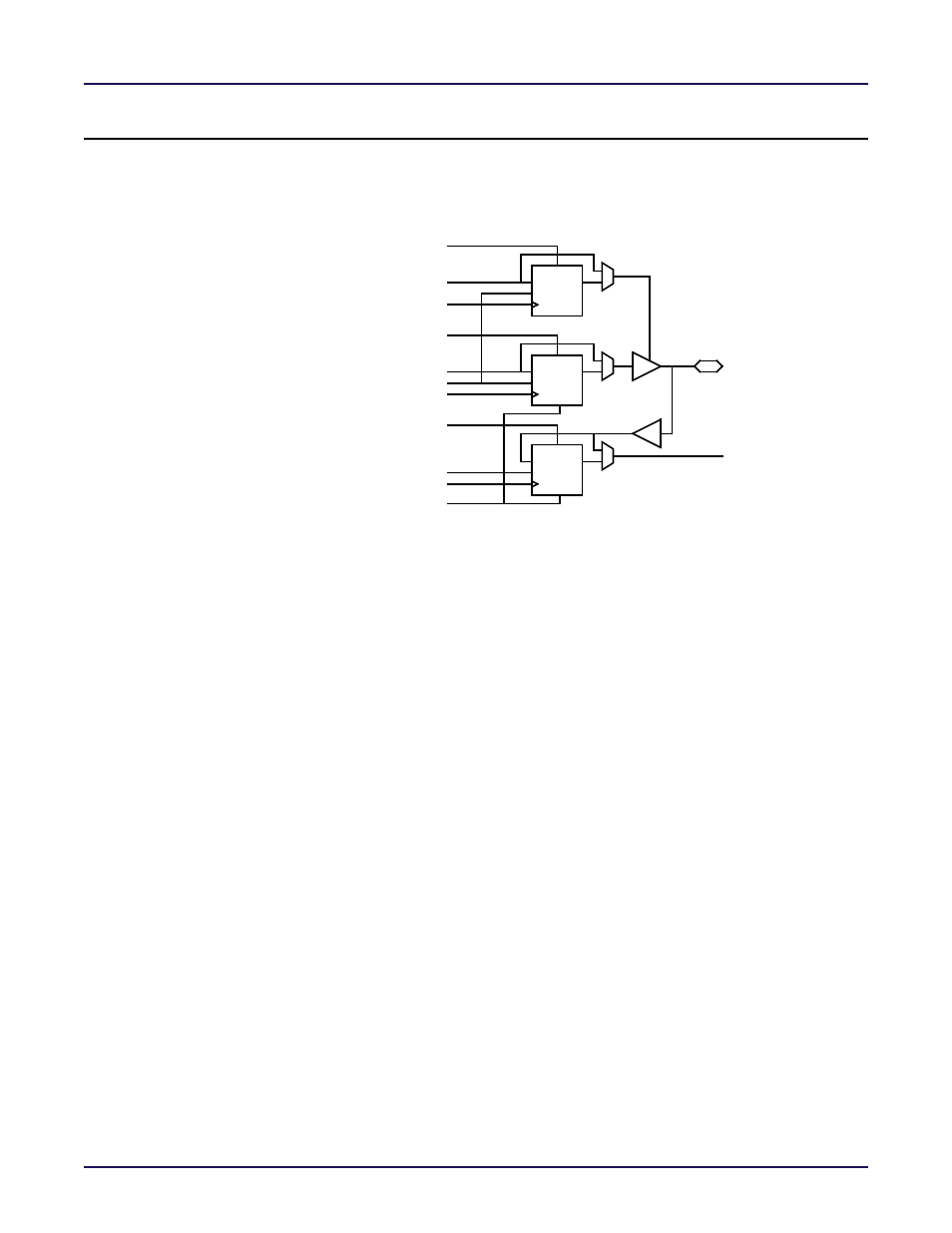

Figure 1-2: IOPAD_D Logic Symbol

IOPAD_D is an I/O pad where each of the transmit, receive, or output enable registers may be

bypassed. The input, output, and output enable registers are all clocked on the rising edge of

their respective clocks. The active‐high oe register is asynchronously cleared upon a low on the

oerstn input. Driving rxrstn low performs an asynchronous initialization of the input register.

The value initialized into the input register is determined by the value of the rstvalue

parameter. Similarly, driving txrstn low performs an asynchronous initialization of the output

register. The value initialized into the output register is also determined by the value of the

rstvalue parameter. Driving srstn low performs a synchronous initialization of both the input

and output registers if the rstmode parameter is set to ʺsyncʺ. The value initialized into the

input and output registers is also determined by the value of the rstvalue parameter. When the

rstmode parameter is set to ʺsyncʺ, the input and output registers have their synchronous reset

inputs active. The synchronous and asynchronous reset capability of the input and output

registers is mutually exclusive. The input and output registers can both have a synchronous or

both have asychronous resets as selected by the rstmode parameter.