Achronix Speedster22i User Macro Guide User Manual

Page 215

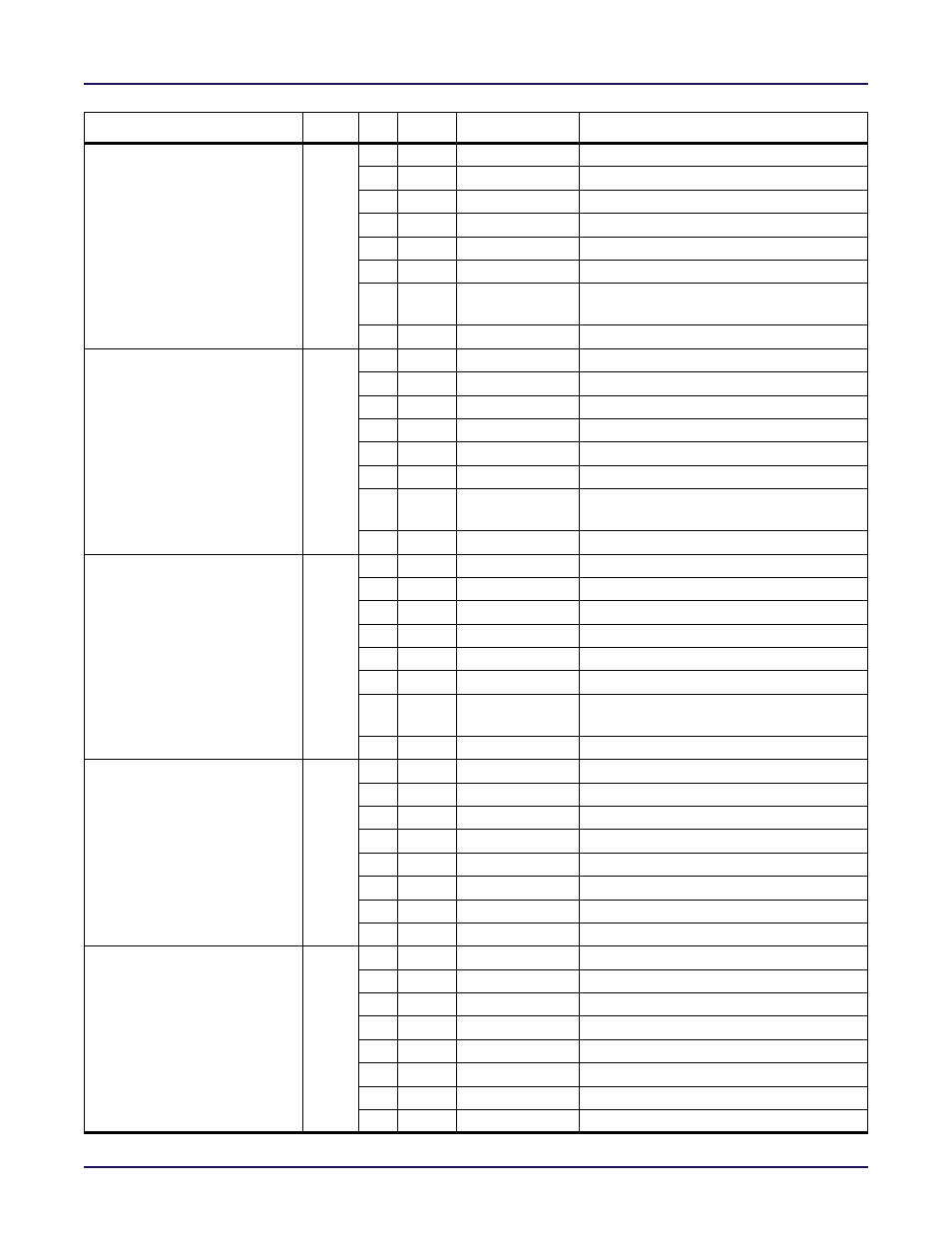

PLL/DLL Clock Generators

ACX_CLKGEN

Speedster Macro Cell Library

PAGE 198

CSR_ADDR_SYNTHOUT1

8’h02

0

in/out

outdiv1[0]

Clkout[1] Output Divider Divisor bit 0

1

in/out

outdiv1[1]

Clkout[1] Output Divider Divisor bit 1

2

in/out

outdiv1[2]

Clkout[1] Output Divider Divisor bit 2

3

in/out

outdiv1[3]

Clkout[1] Output Divider Divisor bit 3

4

in/out

outdiv1[4]

Clkout[1] Output Divider Divisor bit 4

5

in/out

outdiv1[5]

Clkout[1] Output Divider Divisor bit 5

6

in/out

phase_inc[1]

Increments phase of synthesizer clock out-

put by 1/8th of1 period on rising transition

7

in/out

clken_out1

Enable for Clkout[1] Output Synthesizer

CSR_ADDR_SYNTHOUT2

8’h03

0

in/out

outdiv2[0]

Clkout[2] Output Divider Divisor bit 0

1

in/out

outdiv2[1]

Clkout[2] Output Divider Divisor bit 1

2

in/out

outdiv2[2]

Clkout[2] Output Divider Divisor bit 2

3

in/out

outdiv2[3]

Clkout[2] Output Divider Divisor bit 3

4

in/out

outdiv2[4]

Clkout[2] Output Divider Divisor bit 4

5

in/out

outdiv2[5]

Clkout[2] Output Divider Divisor bit 5

6

in/out

phase_inc[2]

Increments phase of synthesizer clock out-

put by 1/8th of1 period on rising transition

7

in/out

clken_out2

Enable for Clkout[2] Output Synthesizer

CSR_ADDR_SYNTHOUT3

8’h04

0

in/out

outdiv3[0]

Clkout[3] Output Divider Divisor bit 0

1

in/out

outdiv3[1]

Clkout[3] Output Divider Divisor bit 1

2

in/out

outdiv3[2]

Clkout[3] Output Divider Divisor bit 2

3

in/out

outdiv3[3]

Clkout[3] Output Divider Divisor bit 3

4

in/out

outdiv3[4]

Clkout[3] Output Divider Divisor bit 4

5

in/out

outdiv3[5]

Clkout[3] Output Divider Divisor bit 5

6

in/out

phase_inc[3]

Increments phase of synthesizer clock out-

put by 1/8th of1 period on rising transition

7

in/out

clken_out3

Enable for Clkout[3] Output Synthesizer

CSR_ADDR_USER_RESERVE_05

8’h05

0

in/out

Reserved

Not Used

1

in/out

Reserved

Not Used

2

in/out

Reserved

Not Used

3

in/out

Reserved

Not Used

4

in/out

Reserved

Not Used

5

in/out

Reserved

Not Used

6

in/out

Reserved

Not Used

7

in/out

Reserved

Not Used

CSR_ADDR_USER_RESERVE_06

8’h06

0

in/out

Reserved

Not Used

1

in/out

Reserved

Not Used

2

in/out

Reserved

Not Used

3

in/out

Reserved

Not Used

4

in/out

Reserved

Not Used

5

in/out

Reserved

Not Used

6

in/out

Reserved

Not Used

7

in/out

Reserved

Not Used

CSR NAME

Addr.

Bit

Type

Initial Value

Description