Heading3 - en_out_reg, Heading3 - reg_initval, Heading3 - reg_srval – Achronix Speedster22i User Macro Guide User Manual

Page 166: Heading3 - reg_rstval, Heading3 - encoder_enable

Memories

BRAM80KECC

Speedster22i Macro Cell Library

PAGE 149

en_out_reg

The en_out_reg parameter enables the register at the output of the BRAM80KECC block. A

value of 1’b0 disables the output register. When the output register is enabled by setting the

en_out_reg to 1’b1, there is an additional cycle of latency for each read operation. The default

value of the en_out_reg parameter is 1’b0.

reg_initval

The reg_initval parameter defines the 40‐bit initial value on the output of the BRAM80KECC

upon application of power to the device. The association of the of the reg_initval parameter

values to the dout,doutp,doutpx bits is assigned according to

reg_initval bit positions to dout,doutp,doutpx

. The default value of reg_initval is 40’h0.

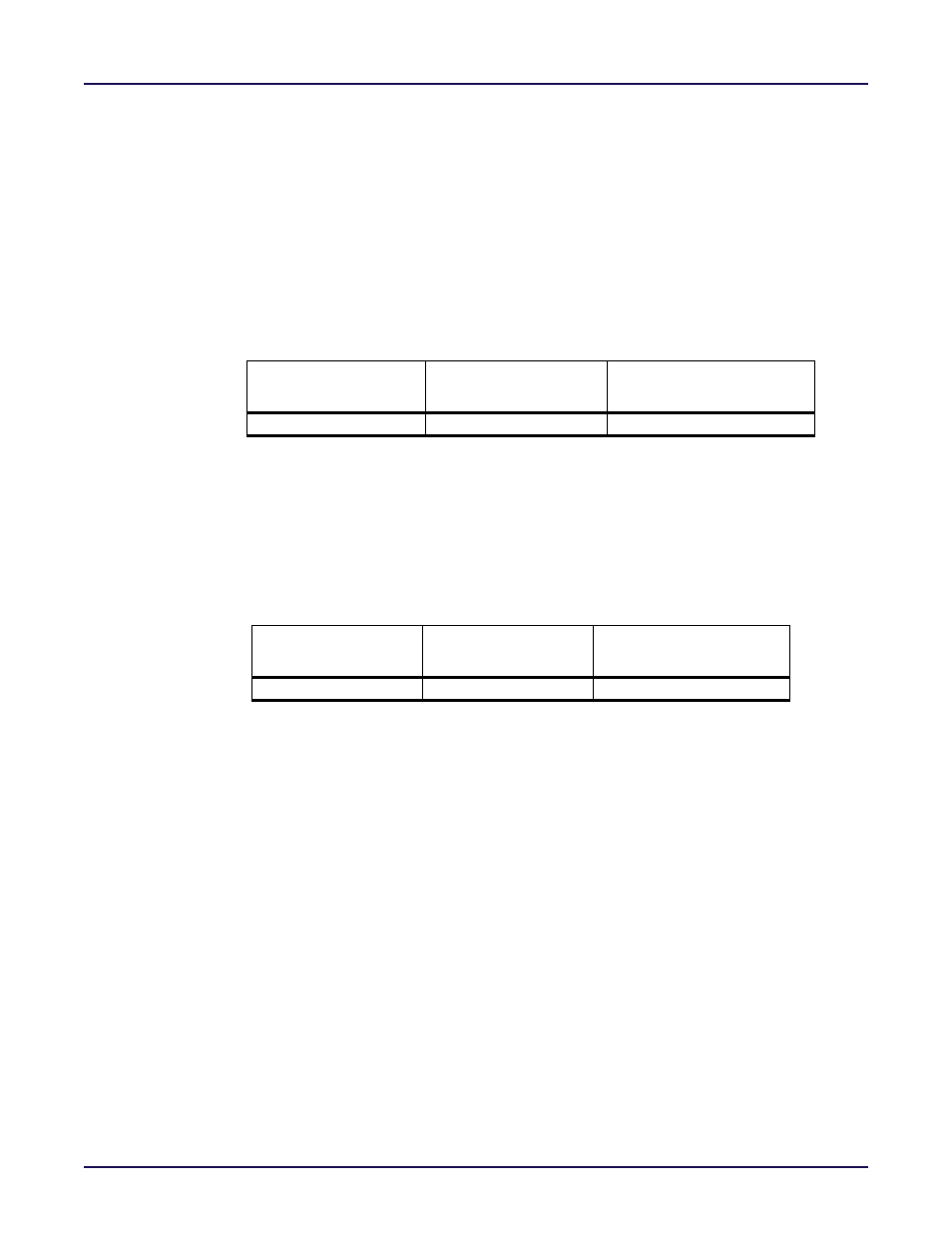

Table 6-43: Relationship of reg_initval bit positions to dout,doutp,doutpx

doutpx

reg_initval[39:36]

doutp

reg_initval[35:32]

dout

reg_initval[31:0]

user_initval[39:36]

user_initval[35:32]

user_initval[31:0]

reg_srval

The reg_srval parameter defines 40‐bit value on the output of the FIFO after a synchronous

reset of the output register. The association of the of the reg_srval parameter values to the

dout,doutp,doutpx bits is assigned according to

Table 6‐44: Relationship of reg_srval bit

positions to dout,doutp,doutpx

The default value of the reg_srval parameter is 40’h0. Note

that this parameter is only relevant when the output register is enabled with the en_out_reg

parameter.

Table 6-44: Relationship of reg_srval bit positions to dout,doutp,doutpx

doutpx

reg_srval[39:36]

doutp

reg_srval[35:32]

dout

reg_srval[31:0]

user_srval[39:36]

user_srval[35:32]

user_srval[31:0]

reg_rstval

The reg_rstval parameter defines the active level of the output register rstreg input. Assigning

a value of 1’b0 to reg_rstval configures the output register to have an active‐low synchronous

reset, while assigning a value of 1’b1 configures the output register to have an active‐high

synchronous reset. The default value of the reg_rstval parameter is 1’b1.

regce_priority

The regce_priority parameter defines the priority of the outregce clock enable input relative to

the rstreg reset input during an assertion of the rstreg signal on the output register. Setting

regce_priority to “rstreg” allows the output register to be set/reset at the next active edge of

the rdclk without requiring a specific value on the outregce output register clock enable input.

Setting regce_priority to “regce” requires that the outregce output register clock enable input

is active for the output register set/reset operation to occur at the next active edge of the rdclk.

encoder_enable

The encoder_enable parameter defines if the ECC encoder circuitry is selected or bypassed.

Setting encoder_enable to 1’b1 enables the ECC encoder for normal operation. Setting

encoder_enable to 1’b0 disables the ECC encoder circuitry and allows the din, dinp, and dinpx

inputs to be connected directly to the memory write port. The default value of the

encoder_enable parameter is 1’b1.