Heading1 - opad, Heading2 - non-registered output pad, Figure - figure 1-14: opad logic symbol – Achronix Speedster22i User Macro Guide User Manual

Page 44: Table - table 1-30: ports, Table - table 1-31: parameters, Table - table 1-32: output function table, Heading3 - verilog instantiation template, Opad, Non-registered output pad

I/O Cells

OPAD

Speedster Macro Cell Library

PAGE 27

OPAD

Non-Registered Output Pad

din

pad

OPAD

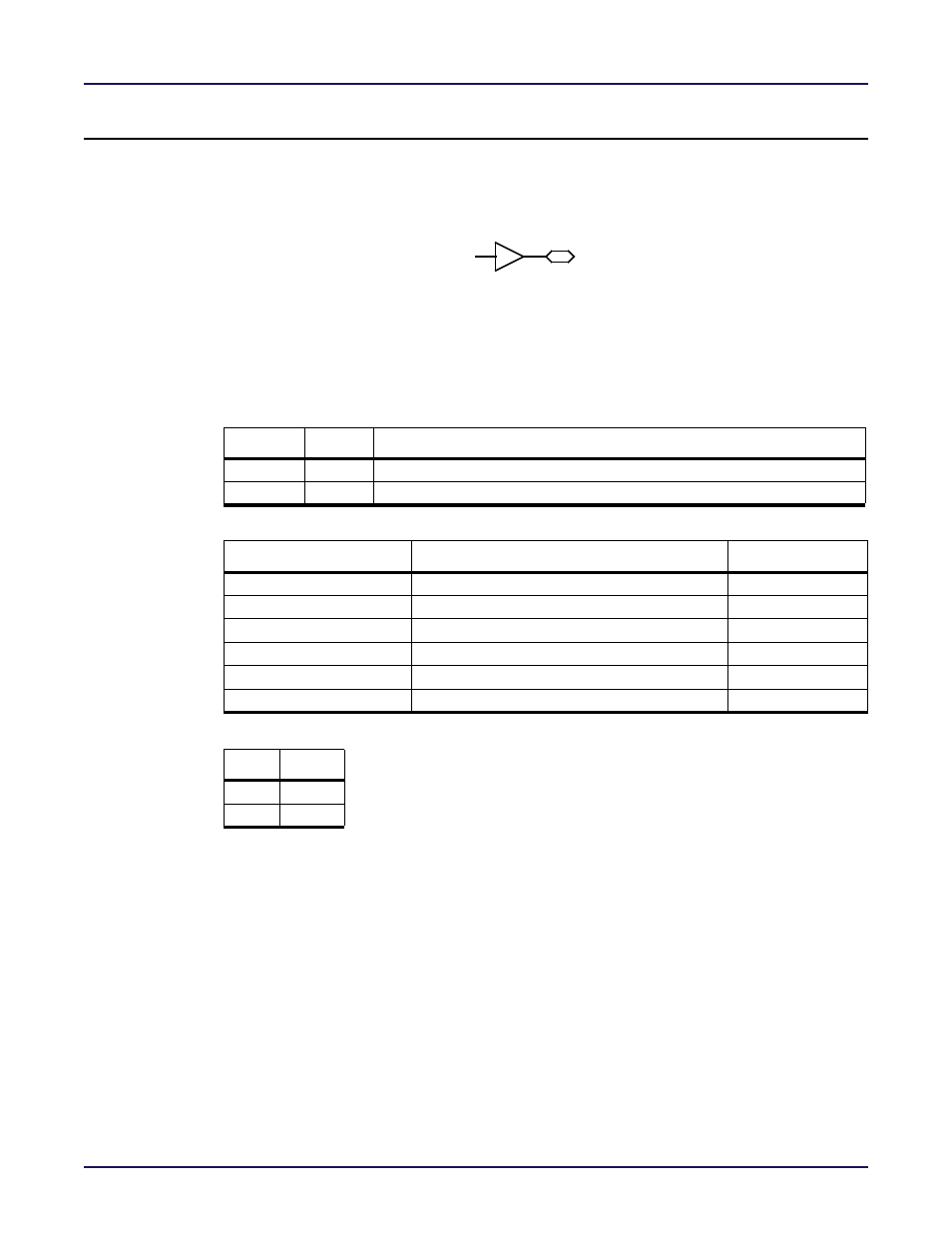

Figure 1-14: OPAD Logic Symbol

OPAD is an non‐registered output pad.

Table 1-30: Ports

Name

Type

Description

din

Data input.

pad

Device output pad. The data at the din input is driven to the pad output.

Table 1-31: Parameters

Parameter

Defined Values

Default Value

location

iostandard

“LVCMOS18”

drive

slew

open_drain

“true”, “false”

“false”

pvt_comp

“none”, “own”

“none”

Table 1-32: Output Function Table

din

pad

Verilog Instantiation Template

OPAD #(.location(""),

.iostandard("LVCMOS18"),

.drive("16"),

.slew("slow"),

.pvt_comp("none"))

instance_name (.din(user_din),

.pad(user_pad));

input

output

“

““

See

"2", "4", "6", "8", "12", "16"

"16"

“fast”, “slow”

“slow”

0

0

1

1