Heading3 - reg_initval, Heading3 - reg_srval – Achronix Speedster22i User Macro Guide User Manual

Page 142

Memories

BRAM80KFIFO

Speedster22i Macro Cell Library

PAGE 125

reg_initval

The reg_initval parameter defines the 40‐bit initial value on the output of the FIFO upon

application of power to the device. The 40‐bit reg_initval parameter assignment is dependent

on the read_width parameter value. The association of the of the reg_initval parameter

values to the dout,doutp,doutpx bits is assigned according to

reg_initval bit positions to dout,doutp,doutpx

. The default value of reg_initval is 40’h0.

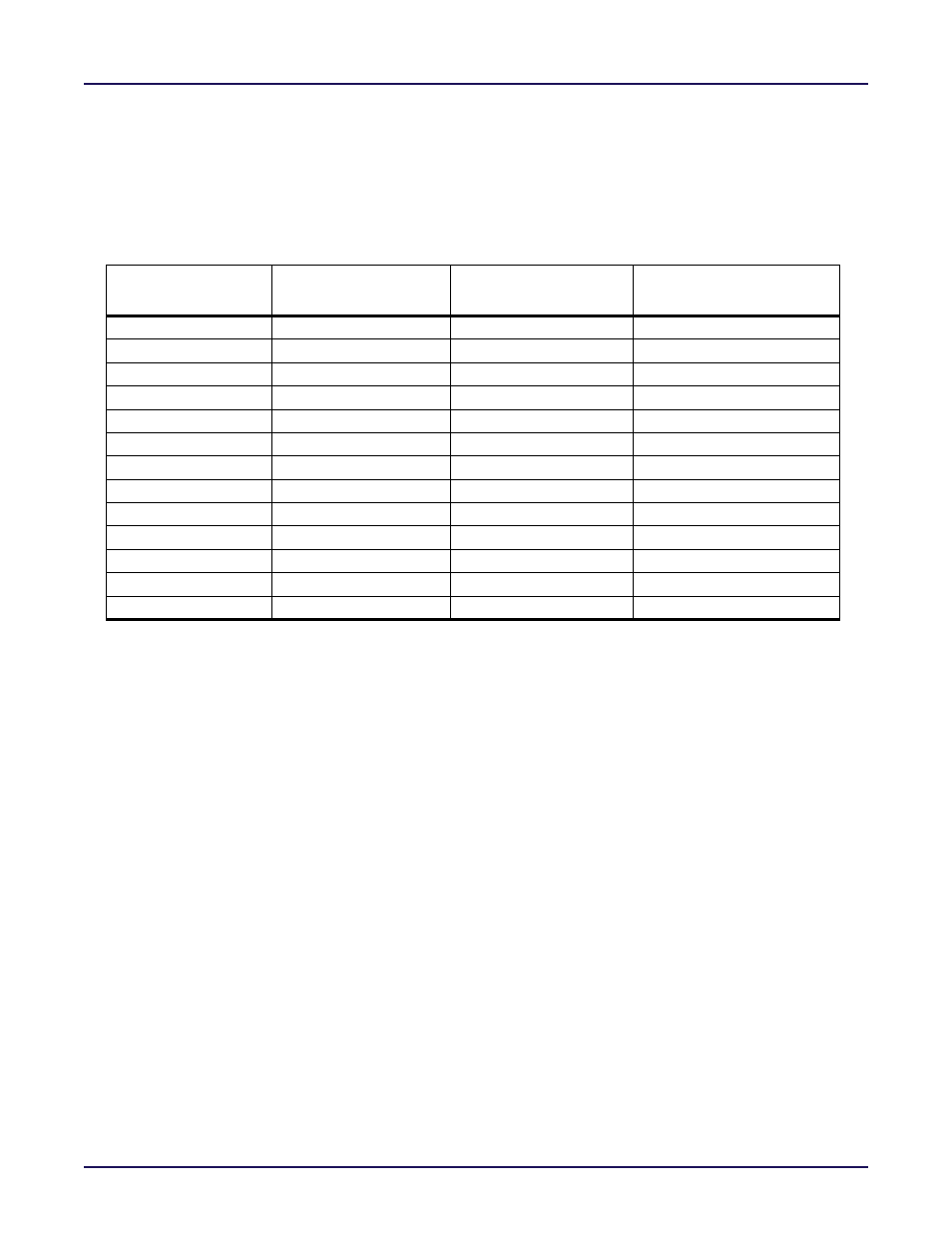

Table 6-24: Relationship of reg_initval bit positions to dout,doutp,doutpx

read_width

doutpx

reg_initval[39:36]

doutp

reg_initval[35:32]

dout

reg_initval[31:0]

40

user_initval[39:36]

user_initval[35:32]

user_initval[31:0]

36

4’hx

user_initval[35:32]

user_initval[31:0]

32

4’hx

4’hx

user_initval[31:0]

20

2’bxx,user_initval[19:18]

2’bxx,user_initval[17:16]

16’hxxxx,user_initval[15:0]

18

4’hx

2’bxx,user_initval[17:16]

16’hxxxx,user_initval[15:0]

16

4’hx

4’hx

16’hxxxx,user_initval[15:0]

10

3’bxxx,user_initval[9]

3’bxxx,user_initval[8]

24’hxxxxxx,user_initval[7:0]

9

4’hx

3’bxxx,user_initval[8]

24’hxxxxxx,user_initval[7:0]

8

4’hx

4’hx

24’hxxxxxx,user_initval[7:0]

5

4’hx

3’bxxx,user_initval[4]

28’hxxxxxxx,user_initval[3:0]

4

4’hx

4’hx

28’hxxxxxxx,user_initval[3:0]

2

4’hx

4’hx

30’hxxxxxxxx,user_initval[1:0]

1

4’hx

4’hx

31’hxxxxxxxx,user_initval[0]

reg_srval

The reg_srval parameter defines 40‐bit value on the output of the FIFO after a synchronous

reset of the output register. The 40‐bit reg_srval parameter assignment is dependent on the

read_width parameter value. The association of the of the reg_srval parameter values to the

dout,doutp,doutpx bits is assigned according to

Table 6‐24: Relationship of reg_initval bit

positions to dout,doutp,doutpx

The default value of the reg_srval parameter is 40’h0. Note

that this parameter is only relevant when the output register is enabled with the en_out_reg

parameter.