Heading2 - acx_clkgen pins, Table - table 9-1: ports, Acx_clkgen pins – Achronix Speedster22i User Macro Guide User Manual

Page 206

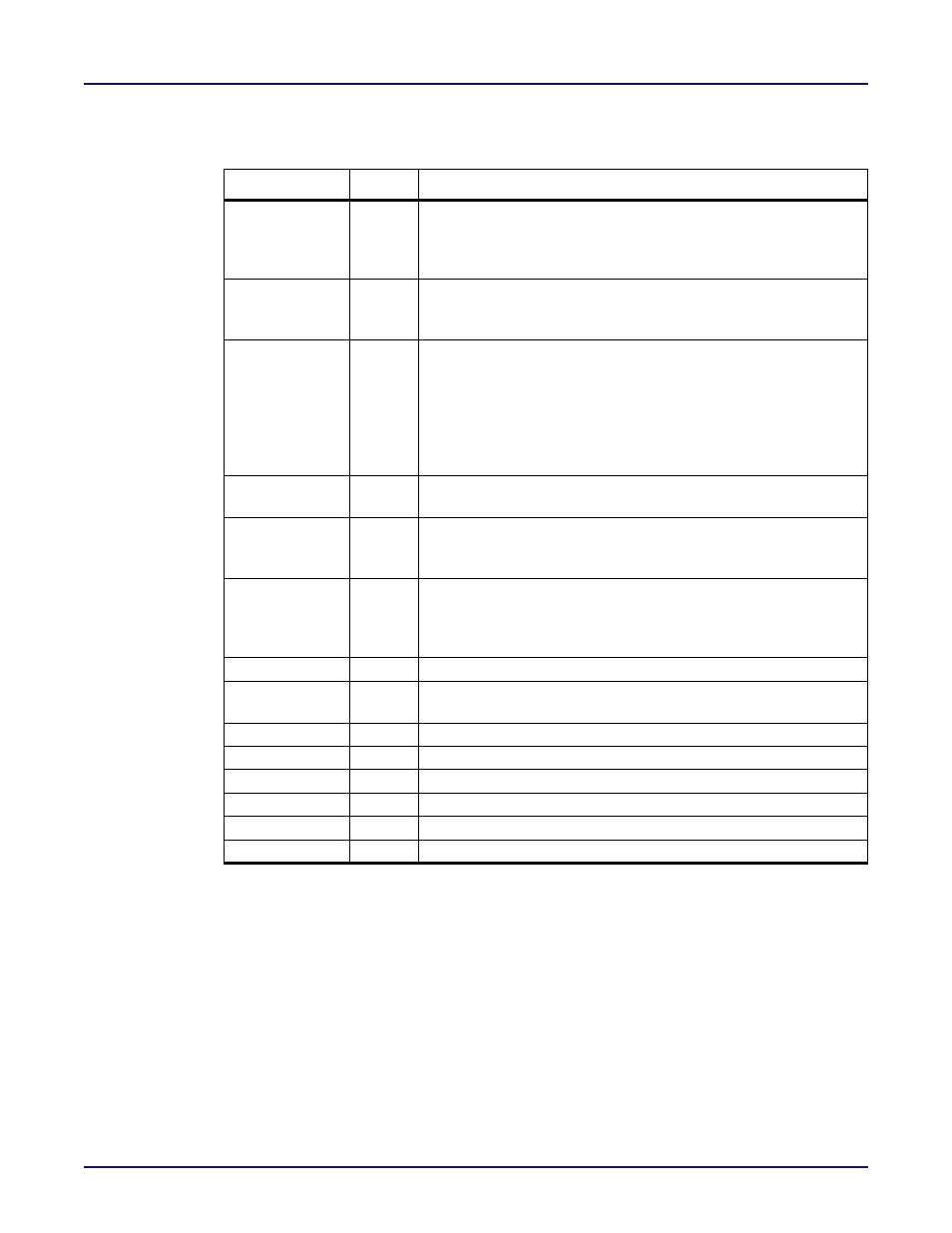

Table 9-1: Ports

Name

Type

Description

refclk

Reference Clock. The reference clock, which is optionally divided

by the Reference Divider, is fed into the Phase Frequency Detector.

The input to the Phase Frequency Detector must be in the range of

30 MHz to 400 MHz.

fbclk

Feedback Clock. The user may connect the Feedback Clock to one

of the generated clkout[3:0] outputs so that the PLL may compen-

sate for the delay of the clock network.

rstn

PLL Reset. Setting the rstn input low will reset the PLL. After return-

ing the rstn input to a high level, the PLL should lock within 500 ref-

clk (after the Reference Divider) clock periods if the PLL is used in

integer divider mode and 1000 clock periods if the PLL is used in

fractional divider mode. The user must hold rstn low for at least one

cycle of the clock frequency input into the Phase Frequency Detec-

tor (after the Reference Divider).

outphrstn

Output Phase Reset. Setting the rstn input low will reset the Phase

Rotator to its initial startup value.

core_clken[3:0]

Clock Output Enable. The core_clken[3:0] controls if the clock out-

puts of the PLL are being driven. Setting the clock enable bit to one

enables the clock output of the corresponding bit position.

phase_inc[3:0]

Clock Phase Increment. A low to high transition of the phase_inc

input increments the phase adjustment of the addressed Phase

Rotator by 1/8th of the VCO frequency. The high period of the

phase_inc signal must be at least at half of the output frequency.

clkout[3:0]

Clock Output.

pll_lock

PLL Lock Status. A high level on the pll_lock signal indicates that

the PLL is locked.

ick_dspll_sif_clk

Serial Control Bus Clock (optional).

ick_dspll_sif_rstn

Serial Control Bus Reset (optional).

ick_sbus_data

Serial Control Bus Data Input (optional).

ick_sbus_req

Serial Control Bus Request (optional).

ock_sbus_ack

Serial Control Bus Acknowledge (optional).

ock_sbus_data

Serial Control Bus Data Output (optional).

PLL/DLL Clock Generators

ACX_CLKGEN

Speedster Macro Cell Library

PAGE 189

ACX_CLKGEN Pins

input

input

input

input

input

input

output

output

input

input

input

input

output

output