Heading2 - bram80kecc pins, Table - table 6-41: bram80kecc pin descriptions, Heading2 - parameters – Achronix Speedster22i User Macro Guide User Manual

Page 165: Table - table 6-42: bram80kecc parameters, Bram80kecc pins, Parameters

Memories

BRAM80KECC

Speedster22i Macro Cell Library

PAGE 148

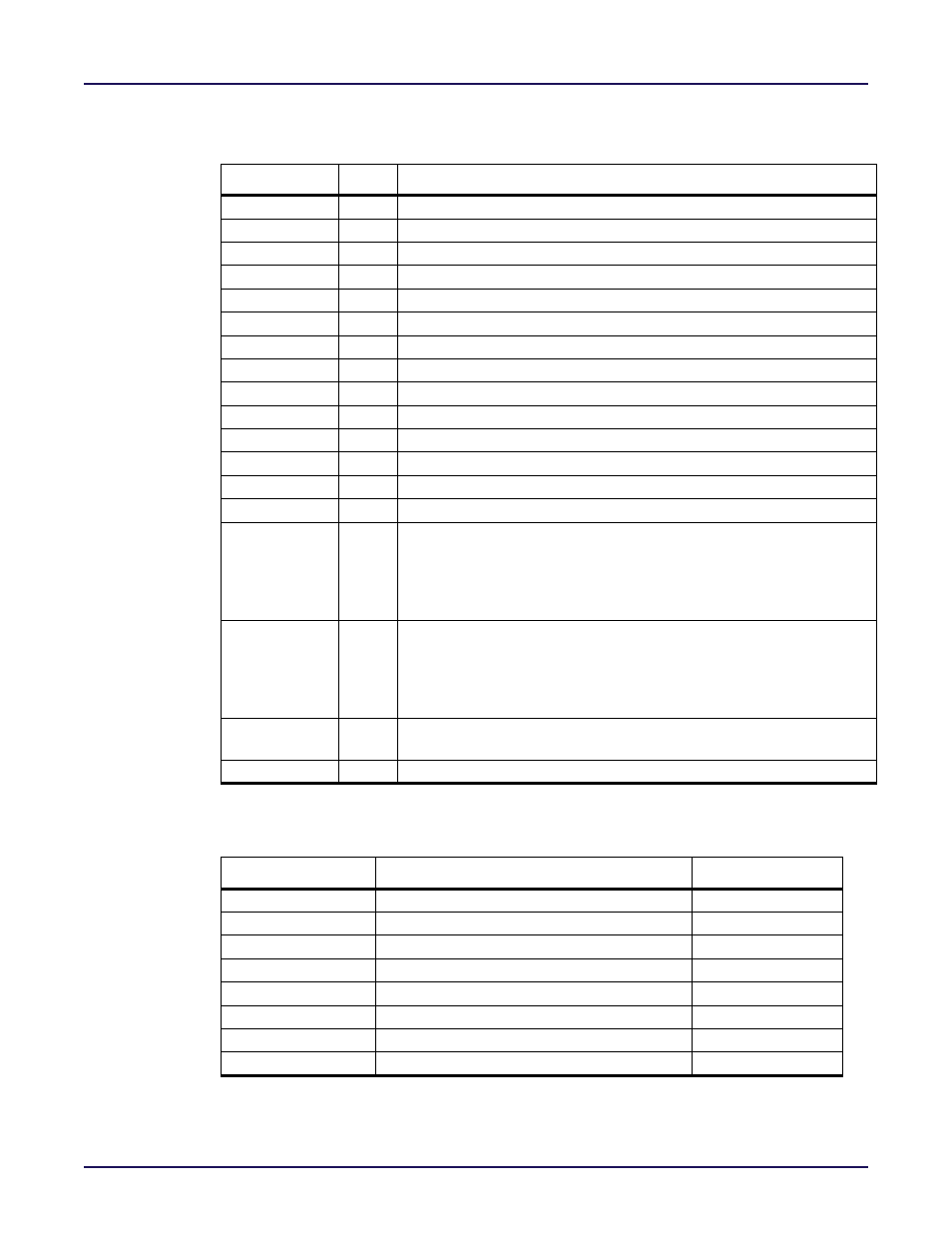

BRAM80KECC Pins

Table 6-41: BRAM80KECC Pin Descriptions

Name

Type

Description

din[31:0]

Write Port Data Input.

dinp[3:0]

Write Port Parity Input (may be used for data).

dinpx[3:0]

Write Port Extended Parity input (may be used for data).

wraddr[10:0]

Write Address.

wren

Write Enable (active-high).

wrclk

Write Clock (programmable, default rising edge = 1’b1).

rdaddr[10:0]

Read Address.

rden

Read Enable (active-high).

rstreg

Output Register Reset (programmable, default active-high).

outregce

Output Register Clock Enable (active-high).

rdclk

Read Clock (programmable, default rising edge = 1’b1).

dout[31:0]

Read Port Data Output.

doutp[3:0]

Read Port Parity Output.

doutpx[3:0]

Read Port Extended Parity Output.

sbit_error

Single Bit Error. (active-high). The sbit_error signal is asserted during a

read operation when a single bit error is detected and the corrected

word is output on the dout pins. The memory contents are not

corrrected by the error correction circuitry. The sbit_error signal is

aligned with the associated read data word.

dbit_error

Double Bit Error. (active-high). The dbit_error signal is asserted during a

read operation when a two-bit error is detected. In the case of a two-bit

error condition, the uncorrected read data word is output on the dout

pins. The dbit_error signal is asserted one cycle after the associated read

data word.

rdaddrecc[10:0]

Read Address. The rdaddrecc output is the 11-bit address of the read

data word.

enc_parity[6:0]

Encoder Parity.

Parameters

Table 6-42: BRAM80KECC Parameters

Parameter

Defined Values

Default Value

en_out_reg

1’b0

reg_initval

40’h0

reg_srval

40’h0

reg_rstval

1’b1

regce_priority

“rstreg”

encoder_enable

1’b1

decoder_enable

1’b1

mem_init_file

“”

input

input

input

input

input

input

input

input

input

input

input

output

output

output

output

output

output

output

1’b0,1’b1

40-bit hexadecimal number

40-bit hexadecimal number

1’b0,1’b1

“rstreg”, ”regce”

1’b0,1’b1

1’b0,1’b1