Heading2 - fifo operations, Heading3 - asynchronous fifo mode reset operation, Fifo operations – Achronix Speedster22i User Macro Guide User Manual

Page 185: Synchronous fifo mode (ptr_sync_mode = 1’b1), Asynchronous fifo mode reset operation

Memories

LRAMFIFO

Speedster22i Macro Cell Library

PAGE 168

Synchronous FIFO Mode (ptr_sync_mode = 1’b1)

The synchronous FIFO standard mode has the advantage that there is no latency in the flag

calculations, so the flags represent the exact state of the FIFO. For synchrous operation, both

wrclk and rdclk must be tied to the same clock signal.

FIFO Operations

Asynchronous FIFO Mode Reset Operation

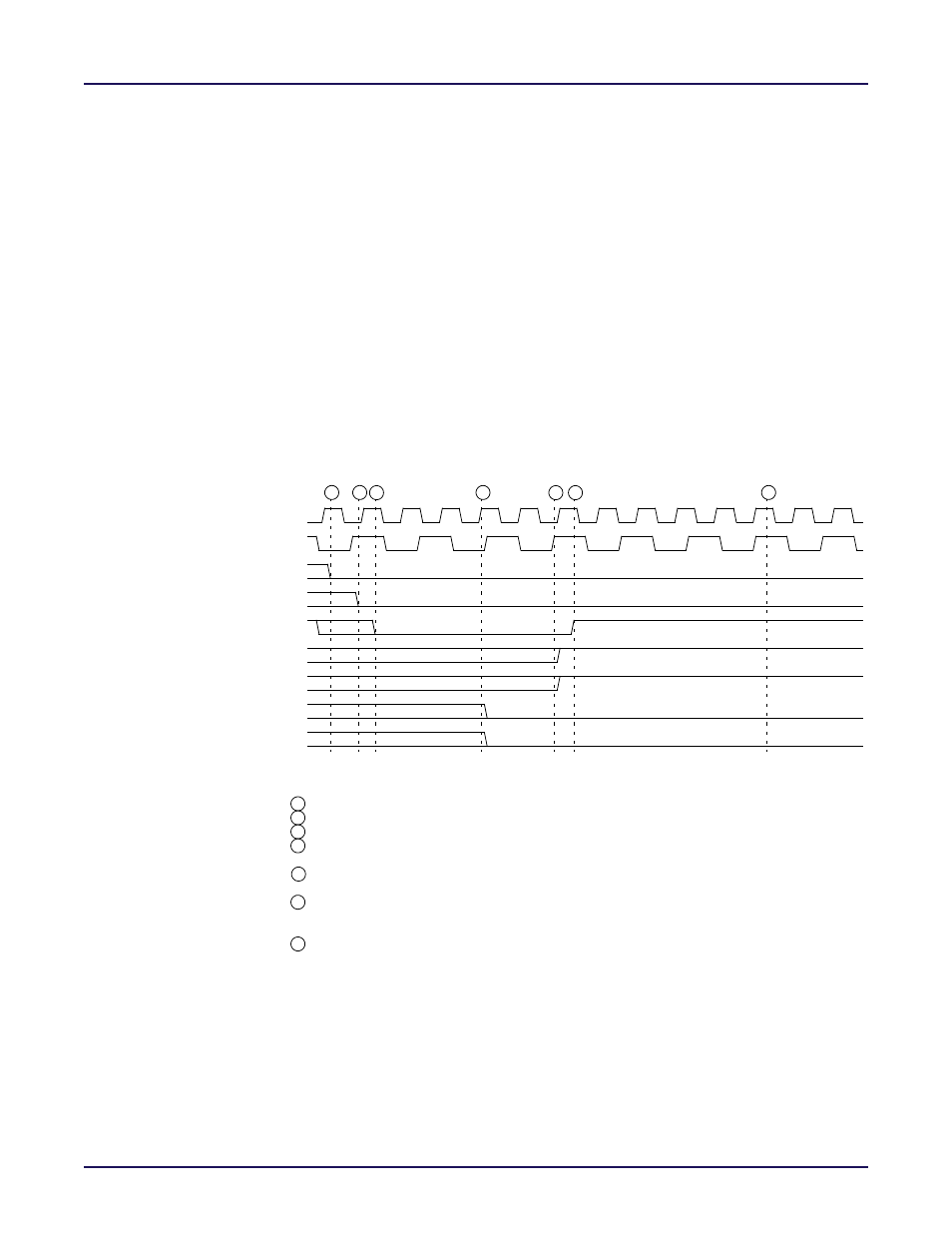

Two options are available to the user with regard to resetting the FIFO. For asychronous FIFO

Reset, the user set rst_sync_mode to 1’b0. To reset the FIFO, the user will assert the rstn signal

for a minimum of three clock cycles of the slower clock cycle between the wrclk and rdclk.

Asserting the reset signal clears both the Write Pointer and Read Pointer, sets the empty and

almost_empty flags, and clears the full and almost_full flags. The user may then release the

rstn signal. The user should not attempt to read or write the FIFO while the rstn input is

asserted or before three cycles after the deassertion of the rstn signal.

6‐37: Asynchronous FIFO Mode Reset Timing Diagram

asychronous reset.

Figure 6-37: Asynchronous FIFO Mode Reset Timing Diagram

wrclk

rdclk

rstn

empty

almost_empty

full

almost_full

wren

rden

1. User reset signal connected to wrrst and rdrst inputs

Note: This timing diagram assumes:

A

B C

Event : The empty and almost_empty flags are asserted (wrrst_sync_stages + 2) active rdclk edges after

Event : The user rstn reset signal is deasserted after a minimum of:

E

F

the rstn input is asserted.

D

G

Event : The user rstn reset signal is asserted.

C

Event : The full and almost_full flags are deasserted (rdrst_sync_stages + 2) active wrclk edges after the

D

rstn input is asserted.

max{(wrrst_sync_stages + 3) rdclk cycles, (rdrst_sync_stages + 3) wrclk cycles}

Event : The first FIFO write operation may begin:

max{(wrrst_sync_stages + 3) rdclk cycles, (rdrst_sync_stages + 3) wrclk cycles}

after the rstn signal is deasserted.

G

E F

Event : The user must disable the wren signal during the reset operation.

A

after the wren and rden inputs are disabled.

Event : The user must disable the rden signal during the reset operation.

B