Heading2 - lram640 pins, Table - table 6-48: lram640 pin descriptions, Heading2 - parameters – Achronix Speedster22i User Macro Guide User Manual

Page 174: Table - table 6-49: lram640 parameters, Lram640 pins, Parameters

Memories

LRAM640

Speedster22i Macro Cell Library

PAGE 157

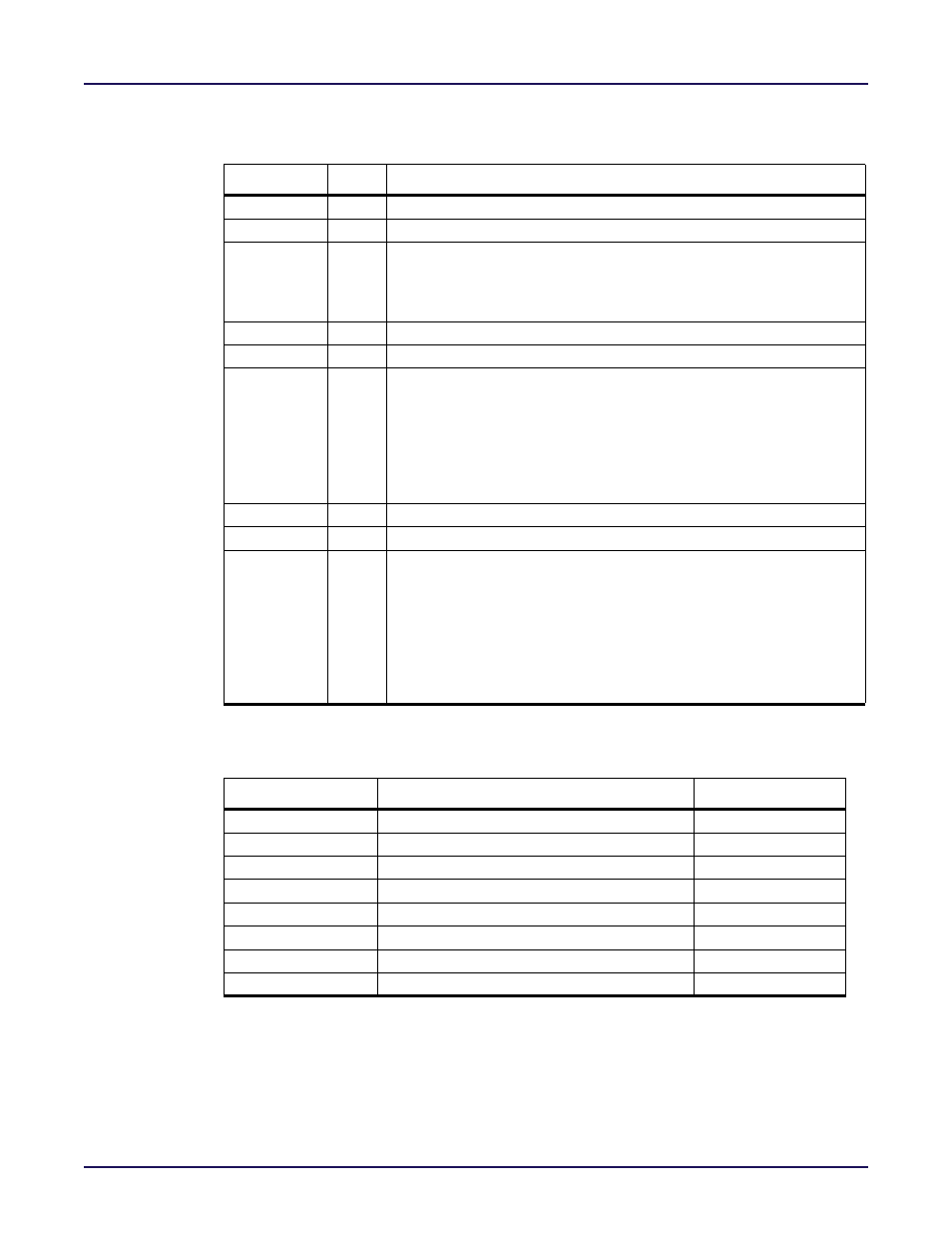

LRAM640 Pins

Table 6-48: LRAM640 Pin Descriptions

Name

Type

Description

wraddr[5:0]

Write Port Address Input.

din[9:0]

Write Port Data Input.

wren

Write Port Enable. (active-high) When the Write Port Enable signal is

asserted, the data present on the Write Port Data Input (din[9:0]) is writ-

ten into the memory location addressed by the Write Port Address input

(wraddr[5:0]) at the next active edge of wrclk.

wrclk

Write Port Clock. (programmable, default rising edge).

rdaddr[5:0]

Read Port Address Input.

rstregn

Read Port Output Register Synchronous Set/Reset (active-low). When

rstregn is asserted, the value of the reg_rstval parameter is written to the

Read Port Output Register upon the next active edge of the rdclk input.

The priority of rstregn input relative to the Read Port Output Register

clock enable (outregce) input is determined by the value of the

regce_priority parameter. The rstregn signal only resets the Read Port

Output register. It does not reset the memory contents.

outregce

Read Port Output Register Clock Enable (active-high).

rdclk

Read Port Clock. (programmable, default rising edge).

dout[9:0]

Read Port Data Output. The Read Port Data Output is configured to be

either synchronous or asynchronous as determined by the reg_dout

parameter. If the reg_dout parameter is set to 1’b0, the Read Port Data

Output reads the contents of the memory addressed by the Read Port

Address onto the dout[9:0] pins. If the reg_dout parameter is set to 1’b1,

the output of the Read Port Data is driven by the contents of the mem-

ory addressed by the Read Port Address at the next active edge of rclk if

the Read Port Output Clock Enable input is high.

Parameters

Table 6-49: LRAM640 Parameters

Parameter

Defined Values

Default Value

write_clock_polarity

“rise“

read_clock_polarity

“rise“

reg_dout

1’b0

reg_initval

10’h0

reg_rstval

10’h0

regce_priority

“rstreg”

mem_init

640’hx

mem_init_file

“”

input

input

input

input

input

input

input

input

output

“rise”, “fall”

“rise”, “fall”

1’b0,1’b1

10-bit binary or hexadecimal value

10-bit binary or hexadecimal value

“rstreg”, ”regce”

640-bit hexadecimal value