Achronix Speedster22i User Macro Guide User Manual

Page 186

Memories

LRAMFIFO

Speedster22i Macro Cell Library

PAGE 169

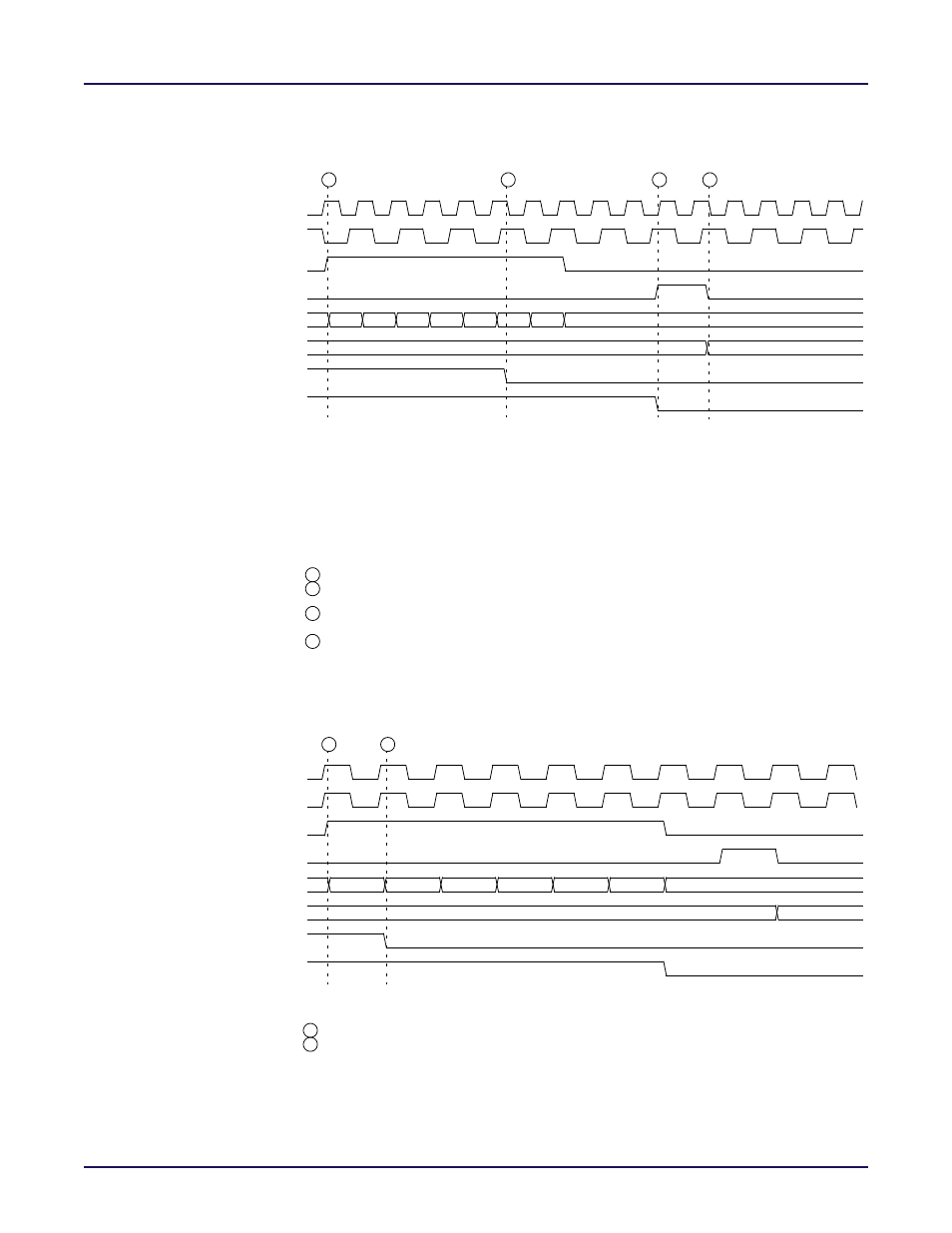

Writing an Empty Asynchronous FIFO (ptr_sync_mode = 1’b0)

Figure 6-38: Writing an Empty Asynchronous FIFO (ptr_sync_mode = 1’b0)

Writing an Empty Synchronous FIFO (ptr_sync_mode = 1’b1)

Figure 6-39: Writing an Empty Synchronous FIFO (ptr_sync_mode = 1’b1)

wrclk

rdclk

wren

rden

din

empty

almost_empty

1. Almost Empty Offset programmed for 5 40-bit words (aempty_offset = 17’h00005)

Note: This timing diagram assumes:

2. wptr_sync_stages = 2’b00

3. ptrsync_mode = 1’b0

wrd 0 wrd 1 wrd 2 wrd 3

dout

wrd 0

wrd 4 wrd 5 wrd 6

A

A

Event : Begin writing 7 words to the FIFO.

Event : empty flag goes inactive one wrclk cycle plus (wrptr_sync_stages + 3) rdclk cycles

after wren becomes active.

B

B

C

D

Previous Read Word

Event : almost_empty flag goes inactive one wrclk cycle plus (wrptr_sync_stages + 3) rdclk cycles

C

after wrd4 (6th word) is written into the FIFO.

D

Event : The first (wrd0) appears at the dout output.

wrclk

rdclk

wren

rden

din

dout

empty

almost_empty

1. Almost Empty Offset programmed for 5 10-bit words (aempty_offset = 7’h06)

Note: This timing diagram assumes:

2. ptr_sync_mode = 1’b1

word 0

word 1

word 2

word 3

word 0

word 4

word 5

A

A

Event : Begin writing 6 words to the FIFO.

Event : empty flag goes inactive one wrclk cycle after wren becomes active.

B

B