Heading2 - fifo operational modes, Fifo operational modes – Achronix Speedster22i User Macro Guide User Manual

Page 184

Memories

LRAMFIFO

Speedster22i Macro Cell Library

PAGE 167

For example, the empty flag is computed from the Synchronized Write Pointer and the Read

Pointer. The write pointer incurs an additional delay of two to five rdclk cyles (set by the

wrptr_sync_stages parameter) before it is used to calculate the empty flag. Therefore, the

empty flag will not transition from the empty to non‐empty state for a minimum of two rdclk

cycles after the first write to the FIFO occurs. A similar delay occurs for the almost_empty flag

as well. Likewise, for the full and almost_full flags, there are two to five wrclk cycles of delay

in the actual FIFO status due to the synchronized read pointer. For an asyncronous FIFO, the

calculation of the flags does not immediately reflect the state of the FIFO. While this behavior

is normal for asynchronous FIFOs, it should be noted.

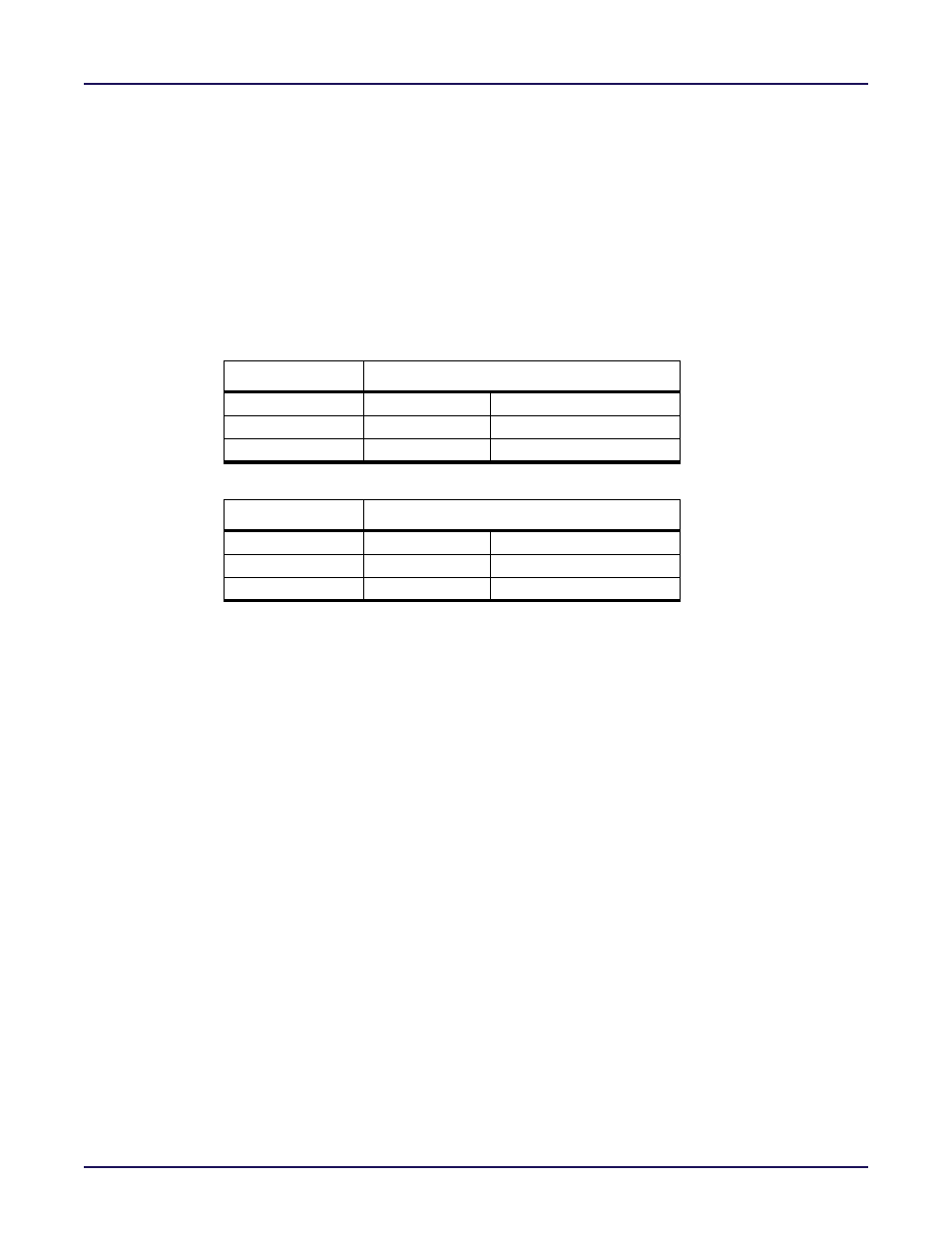

Table 6‐60: Empty and Almost Empty

Flag Latency in Terms of Read Clock Cycles(ptr_sync_mode =1’b0)

Almost Full Flag Latency in Terms of Write Clock Cycles(ptr_sync_mode = 1’b0)

show the

latency for the FIFO flag calculations.

Table 6-60: Empty and Almost Empty Flag Latency in Terms of Read Clock Cycles

FIFO Status Flag

Read Clock Cycle Latency (rdclk cycles)

Flag Assertion

Flag Deassertion

empty flag

0

3 + rdptr_sync_stages

almost empty flag

0

3

(ptr_sync_mode =1’b0)

Table 6-61: Full and Almost Full Flag Latency in Terms of Write Clock Cycles

FIFO Status Flag

Write Clock Cycle Latency (wrclk cycles)

Flag Assertion

Flag Deassertion

full flag

0

3 + wrptr_sync_stages

almost full flag

0

3

(ptr_sync_mode = 1’b0)

Flag Latency in Synchronous Mode (ptr_sync_mode = 1’b1)

A synchronous FIFO has only a single clock, so there is no clock domain crossing required. A

synchronous FIFO has the advantage that the flag calculations are immediate and precise.

FIFO Operational Modes

The FIFO macro supports both single clock synchronous (same clock connected to wrclk and

rdclk inputs without any phase offset between the two clocks) and dual clock asynchronous

(two unrelated clocks or two related clocks) modes of operation. For synchronous operation,

both the wrclk and rdclk inputs must be connected to the same clock net. Phase offsets

between the two clocks in synchronous mode is not allowed. For asynchronous mode, the

user may connect the wrclk and rdclk inputs to two different clocks. The FIFO will treat the

two clocks as if they are unrelated.

Asychronous FIFO Mode (ptr_sync_mode = 1’b0)

After a reset operation, or after the last word has been read from the FIFO, the FIFO will be in

an empty state as indicated by a high level on the empty flag. When the FIFO is set to

asynchronous mode (ptr_sync_mode = 1’b0), the output of the FIFO remains unchanged after

the first write to a FIFO in the empty state. After the first write operation the empty flag will

be deasserted indicating that there is data in the FIFO that may be read. The user must read

the FIFO by setting the rden high at which time the first word written into the FIFO will be

available at the FIFO outputs at the next rising edge of the rdclk input. Each subsequent read

operation updates the FIFO outputs with the next stored data word if it is available (empty

flag = false).