Heading1 - acx_clkgen, Heading2 - phase-locked loop clock generator, Figure - figure 9-1: acx_clkgen logic symbol – Achronix Speedster22i User Macro Guide User Manual

Page 205: Chapter 9 – “pll/dll clock generators, Chapter 9 – pll/dll clock generators, Acx_clkgen, Phase-locked loop clock generator

Speedster Macro Cell Library

PAGE 188

Chapter 9 – PLL/DLL Clock Generators

ACX_CLKGEN

Phase-Locked Loop Clock Generator

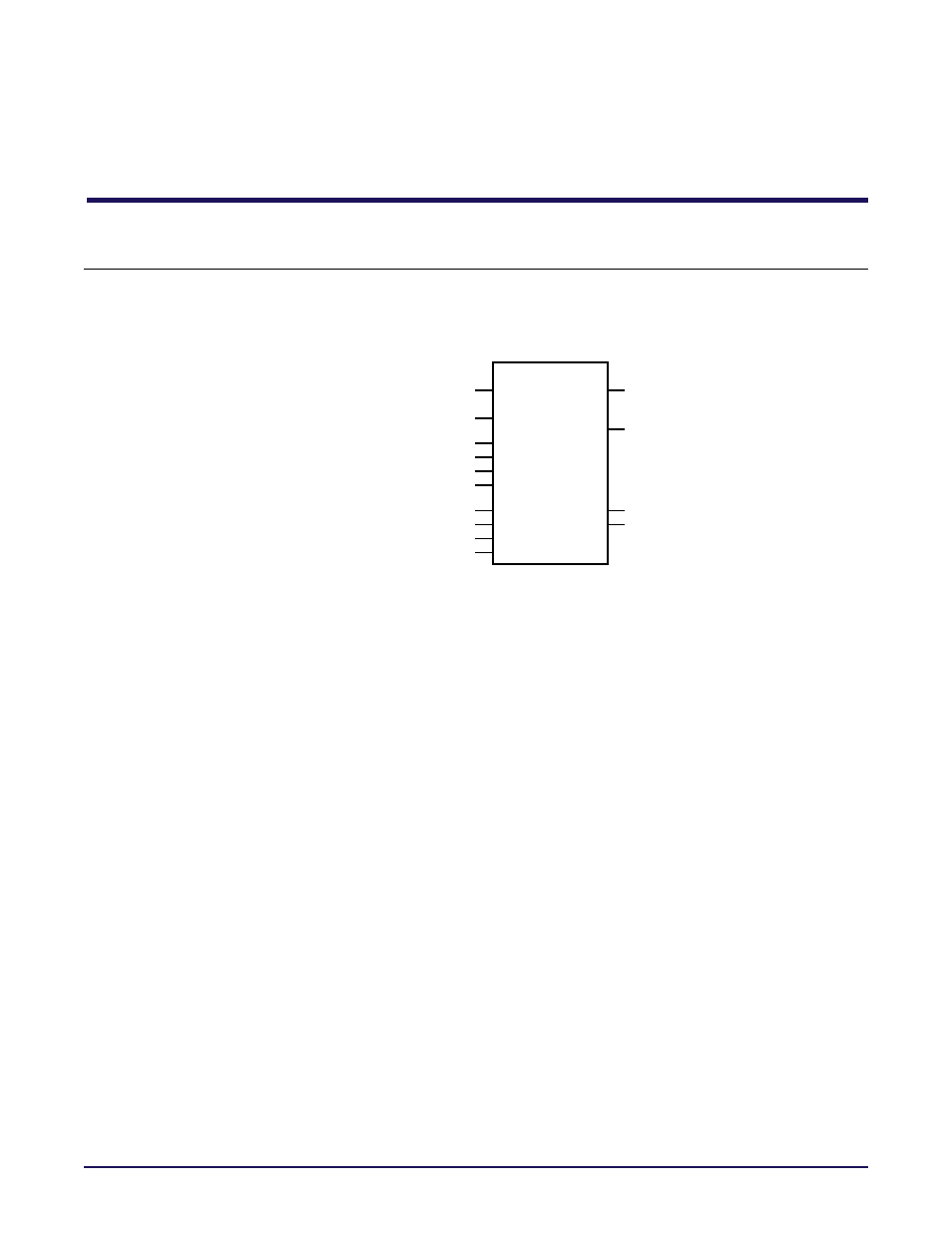

ACX_CLKGEN

refclk

fbclk

clkout[3:0]

pll_lock

rstn

outphrstn

core_clken[3:0]

phase_inc[3:0]

ick_dspll_sif_clk

ick_dspll_sif_rstn

ick_sbus_data[1:0]

ick_sbus_req

ock_sbus_ack

ock_sbus_data[1:0]

Figure 9-1: ACX_CLKGEN Logic Symbol

The reference clock, refclk, is divided by the reference clock divider (6-bit: 1 to 36) before

it is sent to the Phase Frequency Detector (PFD). The PLL charge pump and loop filter

control the VCO to generate full speed clock. The VCO generates 8 equally separated

phases (45 degree separation between adjacent phases). One of the eight phase outputs is

sent to the feedback divider through a multiplexer to allow the PLL running in short loop

operation without de-skew. All 8-phases are sent to 4 phase rotators such that the outputs

of each phase rotator may be independently selectable from any of the 8 phases. Each of

the 4 phase rotator outputs can be shifted dynamically by 1/8

th

of the VCO period in phase

at a time using the phase_inc inputs. All the 4 phases can be reset to the original phase

when the outphrstn input is asserted. The 4 independently selectable phases each go

through an independent output divider (6-bit: 1 to 63) before being sent to the Output

Synthesizer block. One of the 4 output clocks, after going through the clock distribution

tree, may be sent to the feedback divider for de-skew functionality. The feedback divider

has two modes of operations: one is integer mode which offers a range from 2 to 66, while

the other is fractional mode which offers a range from 8 to 66. The fractional mode has 16

bits of resolution.

shows the block diagram of the ACX_CLKGEN block. The

ACX_CLKGEN block may be controlled from the pins and parameter settings or

optionally from the Control Status Registers (CSR) through the Serial Control Bus.