Heading2 - bram80kecc modes of operation, Table - table 6-45: bram80kecc modes of operation, Heading2 - ecc encode/decode operation mode – Achronix Speedster22i User Macro Guide User Manual

Page 168: Heading2 - ecc encode-only operation mode, Heading2 - ecc decode-only operation mode, Bram80kecc modes of operation, Ecc encode/decode operation mode, Ecc encode-only operation mode, Ecc decode-only operation mode

Memories

BRAM80KECC

Speedster22i Macro Cell Library

PAGE 151

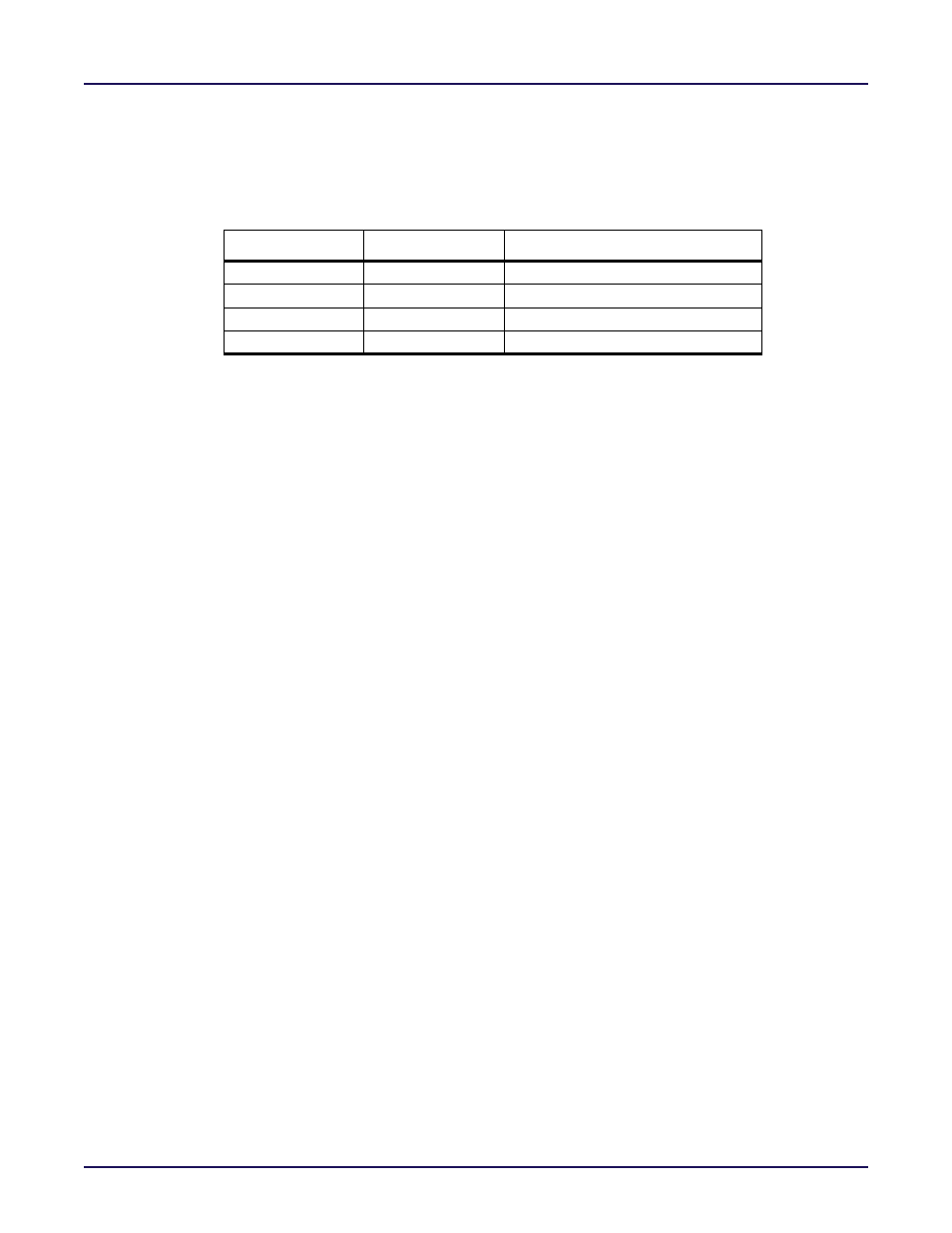

BRAM80KECC Modes of Operation

There are three modes of operation for the BRAM80KECC block defined by the

encoder_enable and decoder_enable parameter shown in

Table 6-45: BRAM80KECC Modes of Operation

encoder_enable

decoder_enable

BRAM80KECC Operation Mode

1’b0

1’b0

Unsupported mode of operation

1’b0

1’b1

ECC decode-only mode

1’b1

1’b0

ECC encode-only mode

1’b1

1’b1

Normal ECC encode/decode mode

ECC Encode/Decode Operation Mode

The ECC Encode/Decode operation mode utilizes both the ECC Encoder and the ECC

Decoder. The 32‐bit user data is written into the memory via the din[31:0] inputs. The ECC

Encoder generates the 7‐bit error correction syndrome and writes it into the memory

alongside the data word via the Parity (dinp) and Extended Parity (dinpx) inputs. During

read operations, the ECC Decoder reads the 32‐bit user data and the 7‐bit syndrome data to

generate an error correction mask. The ECC decoder will correct any single bit error and

detect, but not correct, any two‐bit error. If the ECC decoder detects a single bit error, it

automatically corrects the error and places the corrected data on the dout[31:0] pins as well as

asserts the sbit_error flag. The memory location containing the error is not corrected. If the

ECC decoder detects a two‐bit error, is will place the uncorrected data on the dout[31:0] pins

and assert the dbit_error flag one cycle after the the data word is read.

ECC Encode-Only Operation Mode

The ECC Encode‐Only operation has the ECC Encoder enabled and the ECC Decoder

disabled. This mode allows the user to write the user‐provided 32‐bit data alongside the 7‐bit

error correction syndrome to the memory during write operations. Read operations allow the

user to read the 32‐bit user data alongside the error syndrome directly out of the memory

without correcting the data. The Encode‐Only can be used as a building block to have error

correction for off‐chip memories.

ECC Decode-Only Operation Mode

The ECC Decode‐Only operation has the ECC Encoder disabled and the ECC Decoder

enabled. This mode bypasses the ECC Encoder and allows the user to write 40‐bit data

directly into the BRAM80KECC memory during write operations. Read operations use the

memory’s doutpx[2:0] and doutp[3:0] bits as a 7‐bit syndrome for error correction. The ECC

decoder will correct any single bit error and detect, but not correct, any two‐bit error. If the

ECC decoder detects a single bit error, it automatically corrects the error and places the

corrected data on the dout[31:0] pins as well as asserts the sbit_error flag. The memory

location containing the error is not corrected. If the ECC decoder detects a two‐bit error, is

will place the uncorrected data on the dout[31:0] pins and assert the dbit_error flag one cycle

after the the data word is read. The Encode‐Only can be used as a building block to have error

correction for off‐chip memories.