Achronix Speedster22i User Macro Guide User Manual

Page 216

PLL/DLL Clock Generators

ACX_CLKGEN

Speedster Macro Cell Library

PAGE 199

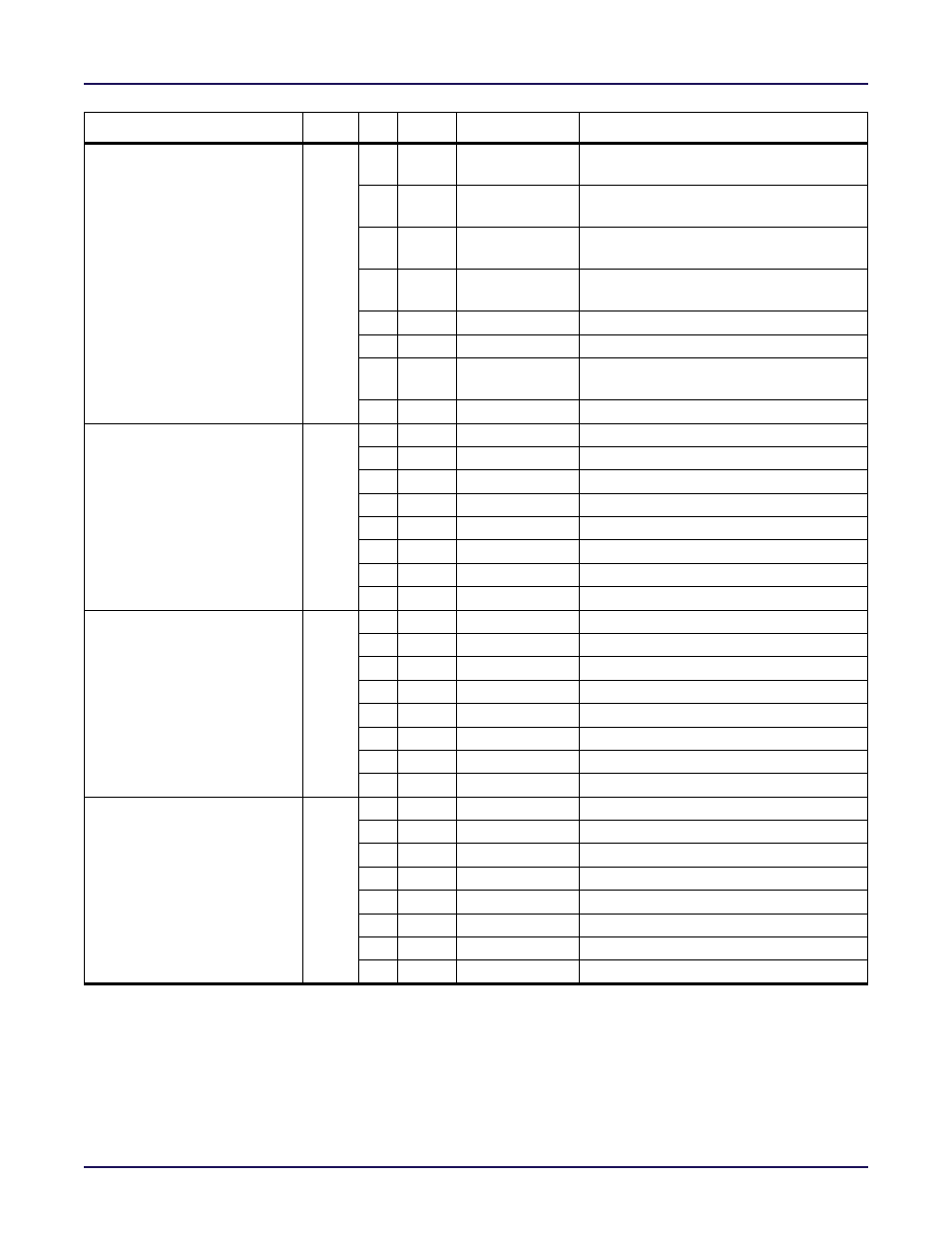

CSR_ADDR_SYNTHOUT_BYPAS

S_RST

8’h07

0

in/out

bypass0

Bypass Clkout[0] synthesizer output with

refclk input

1

in/out

bypass1

Bypass Clkout[1] synthesizer output with

refclk input

2

in/out

bypass2

Bypass Clkout[2] synthesizer output with

refclk input

3

in/out

bypass3

Bypass Clkout[3] synthesizer output with

refclk input

4

in/out

Reserved

Not Used

5

in/out

Reserved

Not Used

6

in/out

outphrst

Resets all phase rotators to initial startup

value (3’h0). Active-high

7

in/out

phaseinc_sat

Mixed Feedback Mode

CSR_ADDR_SYNTHMDIV

8’h08

0

in/out

clkmult[0]

Feedback Divider Divisor Value bit 0

1

in/out

clkmult[1]

Feedback Divider Divisor Value bit 1

2

in/out

clkmult[2]

Feedback Divider Divisor Value bit 2

3

in/out

clkmult[3]

Feedback Divider Divisor Value bit 3

4

in/out

clkmult[4]

Feedback Divider Divisor Value bit 4

5

in/out

clkmult[5]

Feedback Divider Divisor Value bit 5

6

in/out

clkmult[6]

Feedback Divider Divisor Value bit 6

7

in/out

clkmult[7]

Feedback Divider Divisor Value bit 7

CSR_ADDR_SYNTHREFDIV

8’h09

0

in/out

clkdiv[0]

Reference Divider Value bit 0

1

in/out

clkdiv[1]

Reference Divider Value bit 1

2

in/out

clkdiv[2]

Reference Divider Value bit 2

3

in/out

clkdiv[3]

Reference Divider Value bit 3

4

in/out

clkdiv[4]

Reference Divider Value bit 4

5

in/out

clkdiv[5]

Reference Divider Value bit 5

6

in/out

Reserved

Not Used

7

in/out

Reserved

Not Used

CSR_ADDR_SYNTHPROPGAIN

8’h0A

0

in/out

Reserved

Reserved

1

in/out

Reserved

Reserved

2

in/out

Reserved

Reserved

3

in/out

Reserved

Reserved

4

in/out

Reserved

Reserved

5

in/out

Reserved

Reserved

6

in/out

Reserved

Reserved

7

in/out

Reserved

Not Used

CSR NAME

Addr.

Bit

Type

Initial Value

Description