Achronix Speedster22i User Macro Guide User Manual

Page 209

PLL/DLL Clock Generators

ACX_CLKGEN

Speedster Macro Cell Library

PAGE 192

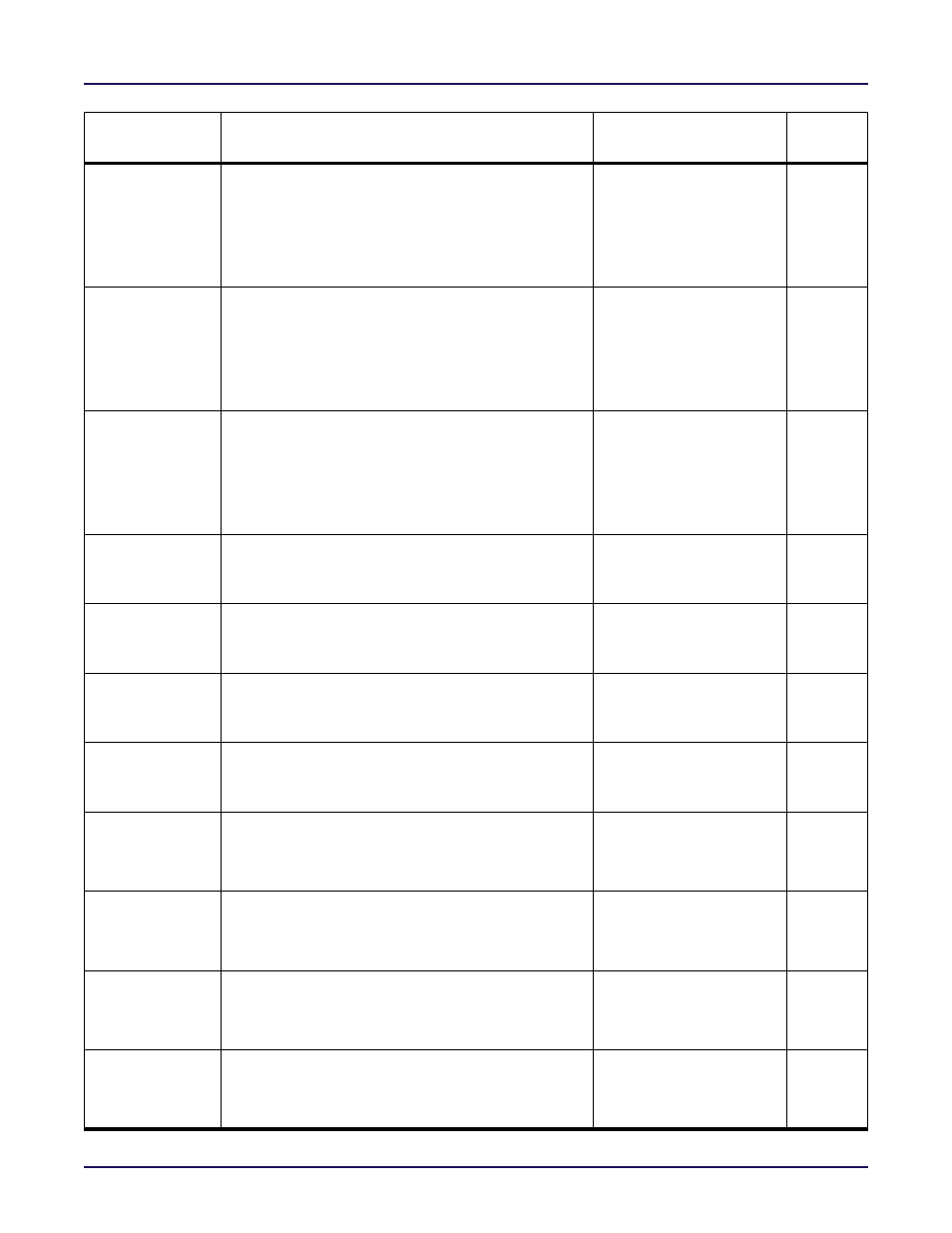

dyn_phase1

Clkout[1] Dynamic Phase Shift Select. If en_phase1 is

enabled,

0: Clkout[1] phase shift determined by static_phase1

parameter.

1: Clkout[1] phase shift determined from the

number of phase_inc[1] rising edges.

1’b0,1’b1

1’b0

dyn_phase2

Clkout[2] Dynamic Phase Shift Select. If en_phase2 is

enabled,

0: Clkout[2] phase shift determined by static_phase2

parameter.

1: Clkout[2] phase shift determined from the

number of phase_inc[2] rising edges.

1’b0,1’b1

1’b0

dyn_phase3

Clkout[3] Dynamic Phase Shift Select. If en_phase3 is

enabled,

0: Clkout[3] phase shift determined by static_phase3

parameter.

1: Clkout[3] phase shift determined from the

number of phase_inc[3] rising edges.

1’b0,1’b1

1’b0

byp_clkdiv0

Clkout[0] Output Synthesizer Bypass.

0: Clkout[0] Output Synthesizer Enabled.

1: Clkout[0] Output Synthesizer Bypassed.

1’b0,1’b1

1’b1

byp_clkdiv1

Clkout[1] Output Synthesizer Bypass.

0: Clkout[1] Output Synthesizer Enabled.

1: Clkout[1] Output Synthesizer Bypassed.

1’b0,1’b1

1’b1

byp_clkdiv2

Clkout[2] Output Synthesizer Bypass.

0: Clkout[2] Output Synthesizer Enabled.

1: Clkout[2] Output Synthesizer Bypassed.

1’b0,1’b1

1’b1

byp_clkdiv3

Clkout[3] Output Synthesizer Bypass.

0: Clkout[3] Output Synthesizer Enabled.

1: Clkout[3] Output Synthesizer Bypassed.

1’b0,1’b1

1’b1

high_cnt0

The output synthesizer divides the PLL output clock by

'high_cnt0 + low_cnt0'. The ratio of high_cnt0 to

'high_cnt0 + low_cnt0' determines the output duty

cycle.

10’h000-10’h3FF

10’h0

low_cnt0

The output synthesizer divides the PLL output clock by

'high_cnt0 + low_cnt0'. The ratio of high_cnt0 to

'high_cnt0 + low_cnt0' determines the output duty

cycle.

10’h000-10’h3FF

10’h0

high_cnt1

The output synthesizer divides the PLL output clock by

'high_cnt1 + low_cnt1'. The ratio of high_cnt1 to

'high_cnt1 + low_cnt1' determines the output duty

cycle.

10’h000-10’h3FF

10’h0

low_cnt1

The output synthesizer divides the PLL output clock by

'high_cnt1 + low_cnt1'. The ratio of high_cnt1 to

'high_cnt1 + low_cnt1' determines the output duty

cycle.

10’h000-10’h3FF

10’h0

Parameter

Description

Defined Values

Default

Value