Heading3 - wrrst_sync_stages, Heading3 - wrptr_sync_stages – Achronix Speedster22i User Macro Guide User Manual

Page 145

Memories

BRAM80KFIFO

Speedster22i Macro Cell Library

PAGE 128

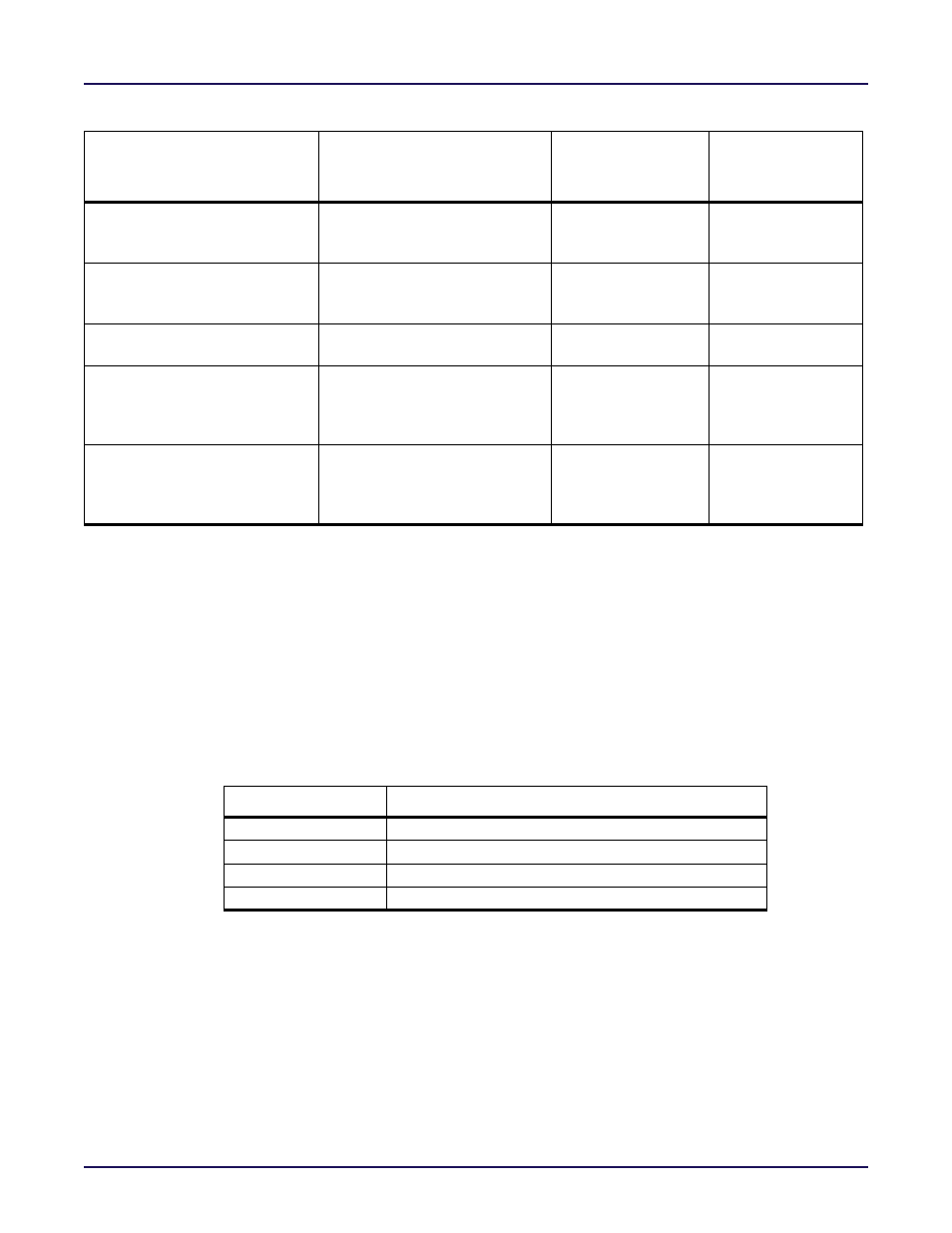

Table 6-27: Reset Usage Model for wrrst and rdrst Inputs

Use Model

Required wrrst and rdrst

connections

Required

wrrst_input_mode

assignment

Required

rdrst_input_mode

assignment

A single reset in the rdclk domain

resets both the read and write

pointers.

The user reset is connected to the

rdrst input. The wrrst signal is tied

inactive.

2’b11

2’b00

A single reset in the wrclk domain

resets both the read and write

pointers.

The user reset is connected to the

wrrst input. The rdrst signal is tied

inactive.

2’b00

2’b11

A single asychronous reset resets

both the read and write pointers.

The user reset is connected to

both the wrrst and rdrst inputs.

2’b11

2’b11

The wrrst reset in the wrclk

domain or the rdrst reset in the

rdclk domain resets both the read

and write pointers.

The user reset in the wrclk domain

is connected to the wrrst input.

The user reset in the rdclk domain

is connected to the rdrst input.

2’b10

2’b10

The wrrst reset in the wrclk

domain resets the write pointer.

The rdrst reset in the rdclk domain

resets the read pointer.

The user reset in the wrclk domain

is connected to the wrrst input.

The user reset in the rdclk domain

is connected to the rdrst input.

2’b00

2’b00

wrrst_sync_stages

The wrrst_sync_stages parameter defines the number of stages of registers used to

synchronize the wrrst input pin to the rdclk clock domain if the wrrst signal is used by the

Read Pointer Reset. The value of the wrrst_sync_stages parameter is only used if the

rdrst_input_mode is set to 2’b10 or 2’b11. The mapping of the wrrst_sync_stages parameter

value to the number of sychronization stages is defined in

wrrst_sync_stages Parameter Settings to Synchronization Stage Depth

, where each stage

corresponds to a register in the Write Reset Synchronizer shown in

Write Pointer Reset Input Selection Block Diagram

. For example, setting wrrst_sync_stages

to 2’b00 configures the wrrst synchronization circuit to have two back‐to‐back registers in the

Write Reset Synchonizer. The default value of the wrrst_sync_stages parameter is 2’b00.

Table 6-28: Mapping wrrst_sync_stages Parameter Settings to Synchronization Stage Depth

wrrst_sync_stages

Write Reset Synchronization Stage Depth

2’b00

2

2’b01

3

2’b10

4

2’b11

5

wrptr_sync_stages

The wrptr_sync_stages parameter defines the number of stages used in the Write Pointer

Synchonizer circuit that synchronizes the Write Pointer to the rdclk clock domain. When the

FIFO is in asynchronous mode, (sync_mode = 1’b0), the output of the synchonized Write

Pointer is compared to the Read Pointer to generate the empty and almost_empty flags. The

synchronized Write Pointer may also be routed to the wrcounter output (wrcount_sync_mode

= 1’b0). The mapping of the wrptr_sync_stages parameter value to the number of sychro‐

nization stages is defined in

Table 6‐29: Mapping wrptr_sync_stages Parameter Settings to

, where each stage corresponds to a register in the Write Pointer

Synchronizer circuit shown in

Figure 6‐10: Write Pointer Synchronizer Block Diagram

Higher values for the wrptr_sync_stages parameter reduce the possibility of a metastable