Heading2 - parameters, Table - table 6-16: bram80kfifo parameters, Heading3 - sync_mode – Achronix Speedster22i User Macro Guide User Manual

Page 138: Heading3 - write_width, Parameters

Memories

BRAM80KFIFO

Speedster22i Macro Cell Library

PAGE 121

Parameters

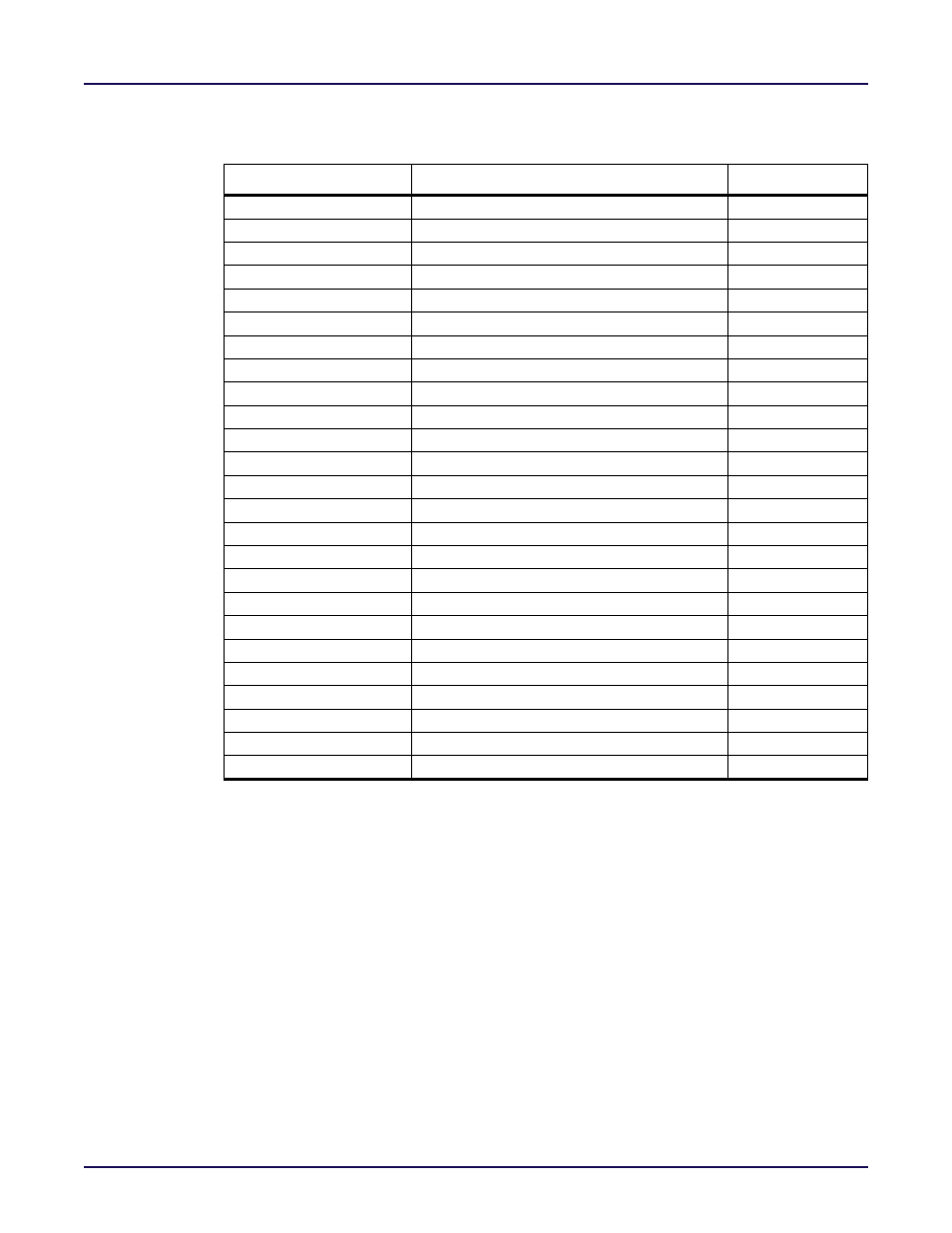

Table 6-16: BRAM80KFIFO Parameters

Parameter

Defined Values

Default Value

sync_mode

1’b0

write_width

40

read_width

40

fwft

1’b0

en_out_reg

1’b1

reg_initval

40’h0

reg_srval

40’h0

reg_rstval

1’b1

regce_priority

“rstreg”

wrrst_rstval

1’b1

wrrst_input_mode

2’b10

wrrst_sync_stages

2’b00

wrptr_sync_stages

2’b00

rdrst_rstval

1’b1

rdrst_input_mode

2’b10

rdrst_sync_stages

2’b00

rdptr_sync_stages

2’b00

wrcount_sync_mode

1’b1

rdcount_sync_mode

1’b1

afull_offset

17’h00004

aempty_offset

17’h00004

wren_polarity_sel

1’b1

rden_polarity_sel

1’b1

en_rd_when_empty

1’b0

en_wr_when_full

1’b0

sync_mode

The sync_mode parameter is used to bypass the synchronization circutry between the read

and write ports when both ports are connected to the same clock. If both the wrclk and rdclk

clock inputs are connected to the same clock without any phase difference between the rdclk

and wrclk inputs, the user may set the sync_mode parameter to 1’b1 to allow faster updates to

the status flags (empty, full, etc.). If the read and write clocks are connected to different clocks,

the synchronization circutry must be used and the sync_mode parameter must be set to 1’b0.

The default value of the sync_mode parameter is 1’b0.

write_width

The write_width parameter defines the width of the data input bus of the FIFO from one to

forty bits according to the allowed values defined in

Table 6‐16: BRAM80KFIFO Parameters

Table 6‐17: FIFO write_width versus Maximum Write Depth

defines the maximum depth of

the FIFO for each of the valid values of the write_width parameter. The default value of the

write_width parameter is 40’h0.

1’b0, 1’b1

1, 2, 4, 5, 8, 9, 10, 16, 18, 20, 32, 36, 40

1, 2, 4, 5, 8, 9, 10, 16, 18, 20, 32, 36, 40

1’b0, 1’b1

1’b0, 1’b1

40-bit hexadecimal number

40-bit hexadecimal number

1’b0, 1’b1

“rstreg”, “regce”

1’b0, 1’b1

2’b00, 2’b01, 2’b10, 2’b11

2’b00, 2’b01, 2’b10, 2’b11

2’b00, 2’b01, 2’b10, 2’b11

1’b0, 1’b1

2’b00, 2’b01, 2’b10, 2’b11

2’b00, 2’b01, 2’b10, 2’b11

2’b00, 2’b01, 2’b10, 2’b11

1’b0, 1’b1

1’b0, 1’b1

17-bit hexadecimal number

17-bit hexadecimal number

1’b0, 1’b1

1’b0, 1’b1

1’b0, 1’b1

1’b0, 1’b1