Heading1 - opad_diff, Heading2 - non-registered differential output pad, Figure - figure 1-18: opad_diff logic symbol – Achronix Speedster22i User Macro Guide User Manual

Page 52: Table - table 1-39: ports, Table - table 1-40: parameters, Table - table 1-41: output function table, Heading3 - verilog instantiation template, Opad_diff, Non-registered differential output pad

I/O Cells

OPAD_DIFF

Speedster Macro Cell Library

PAGE 35

OPAD_DIFF

Non-Registered Differential Output Pad

din

pad

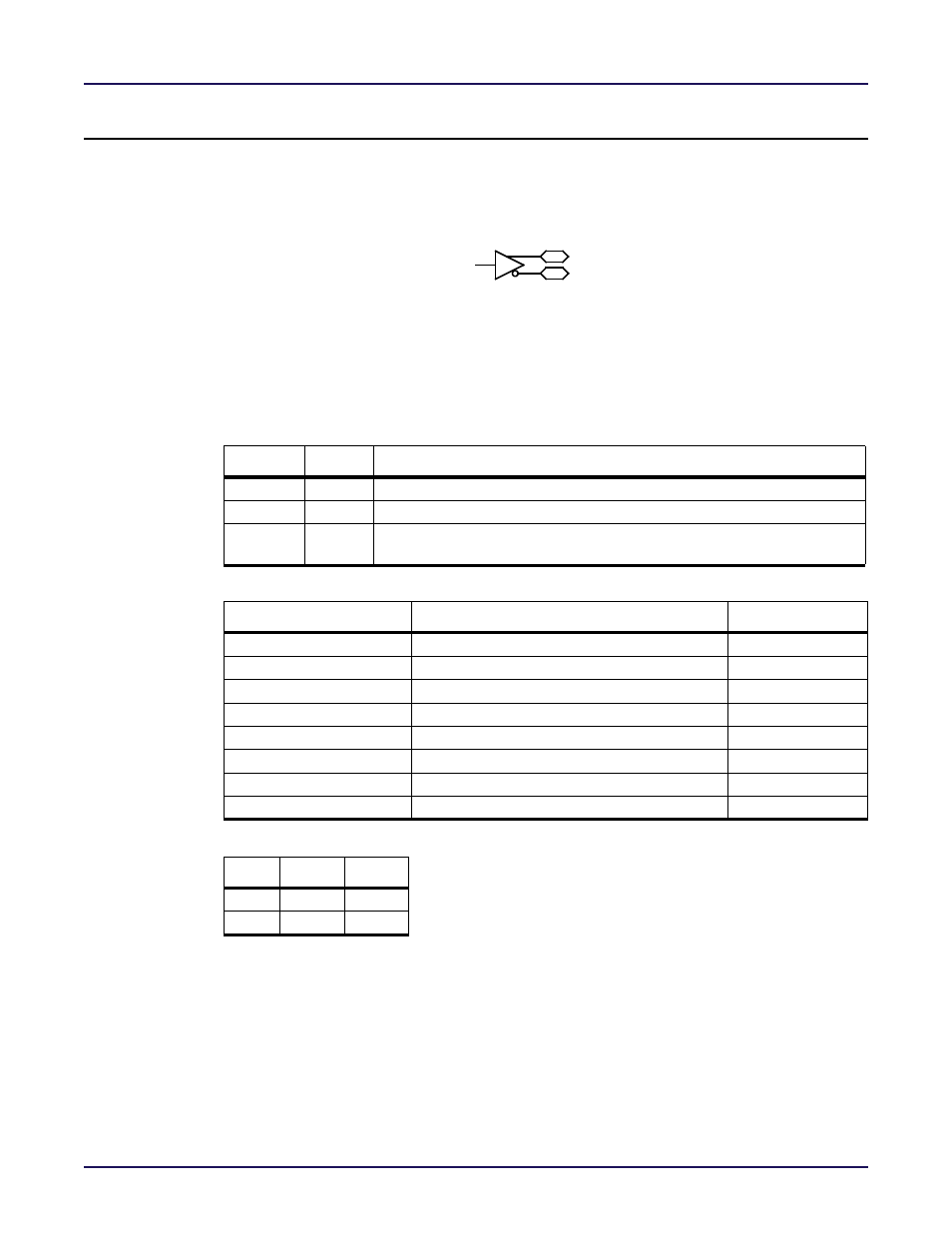

OPAD_DIFF

padn

Figure 1-18: OPAD_DIFF Logic Symbol

OPAD_DIFF is an asynchronous differential output pad with input din and outputs pad and

padn.

Table 1-39: Ports

Name

Type

Description

din

Data input.

pad

Device output pad. The data at the din input is driven to the pad output.

padn

Device complement output pad. The logical inverse of the data at the din

input is driven to the padn output.

Table 1-40: Parameters

Parameter

Defined Values

Default Value

locationp

locationn

iostandard

“LVDS”

drive

slew

open_drain

“true”, “false”

“false”

pvt_comp

“none”, “own”

“none”

invert_out

“off”,”on”

“off”

Table 1-41: Output Function Table

din

pad

padn

Verilog Instantiation Template

OPAD_DIFF #(.locationp(""),

.locationn(""),

.iostandard("LVDS"),

.drive("16"),

.slew("slow"),

.invert_out(“off”),

.open_drain(“false”),

.pvt_comp("none"))

input

output

output

“

““

“

““

See

"2", "4", "6", "8", "12", "16"

"16"

“fast”, “slow”

“slow”

0

0

1

1

1

0