Heading3 - initpx_00 – initpx_31, Memory organization and data input / output pin, Assignments – Achronix Speedster22i User Macro Guide User Manual

Page 112

Memories

BRAM80K

Speedster22i Macro Cell Library

PAGE 95

initpx_00 – initpx_31

The initpx_00 through initpx_31 parameters define the initial contents of the memory contents

associated with doutpxa[3:0] and doutpxb[3:0]. Each 256‐bit parameter associated with the

BRAM80K memory is defined in the

Memory Organization and Data Input / Output Pin Assignments

The BRAM80K memory block supports memory widths from one to forty bits wide. The

width

of

the

dina(dinb)

data

input

is

determined

by

the

porta_write_width(portb_write_width) parameter while the width of the douta(doutb) data

output is determined by the porta_read_width(portb_read_width) parameter. The width of

read port may be set to be different from the width of the write port on a per‐port basis.

Additionally, the width of the Port A read/write may be set to be different from the Port B

read/write widths. There are, however, some limitations of the port width assignments

between the read and write width assignments as well as the Port A and Port B width

assignments. The valid port widths defined in

may be

divided into three groups:

•

Group1 (n x 5 widths): 40, 20, 10, 5

•

Group2 (n x 9 widths): 36, 18, 9

•

Group3 (n x 2 widths): 32, 16, 8, 4, 2, 1

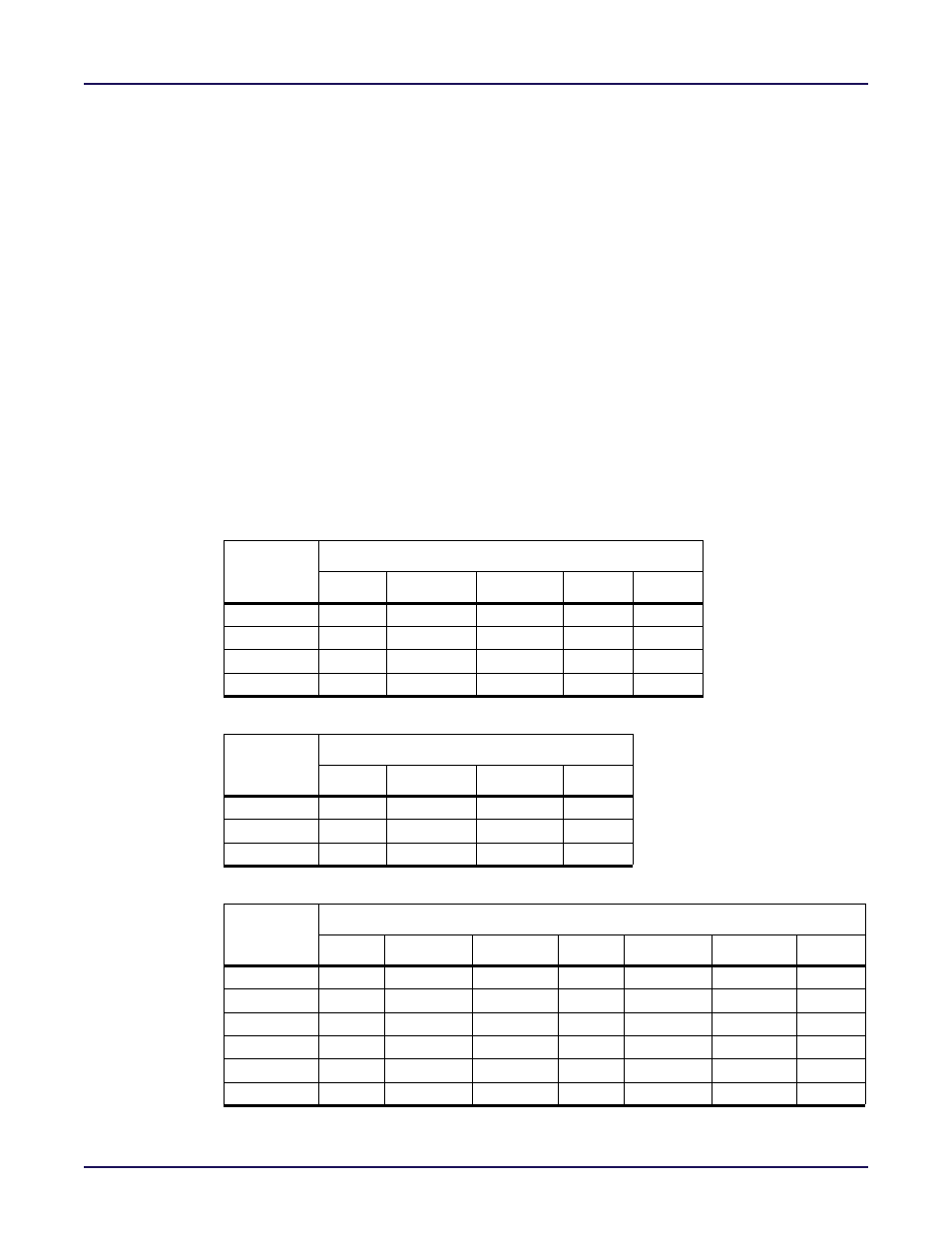

Table 6-5: Valid Port A Width Versus Port B Width Combinations per port for n x 5 width modes

Port A

Width

Port B Width

2kx40

4kx20

8kx10

16kx5

Other

40

20

10

5

Table 6-6: Valid Port A Width Versus Port B Width Combinations per port for n x 9 width modes

Port A

Width

Port B Width

2kx36

4kx18

8kx9

Other

36

18

9

Table 6-7: Valid Port A Width Versus Write Port B Combinations per port for n x 2 width modes

Port A

Width

Port B Width

2kx32

4kx16

8kx8

16kx4

32kx2

64kx1

Other

32

16

8

4

2

1

–

–

–

–

–

–

–

–

–

–

–

–

–