Heading1 - ipad_diffd, Figure - figure 1-11: ipad_diffd logic symbol, Table - table 1-25: ports – Achronix Speedster22i User Macro Guide User Manual

Page 39: Table - table 1-26: parameters, Ipad_diffd

I/O Cells

IPAD_DIFFD

Speedster Macro Cell Library

PAGE 22

IPAD_DIFFD

Registered Differential Input Pad with Asynchronous or Synchronous

Set/Reset

q

ce

d

rstn

dout

pad

clk

data_en

rstn

IPAD_DIFFD

padn

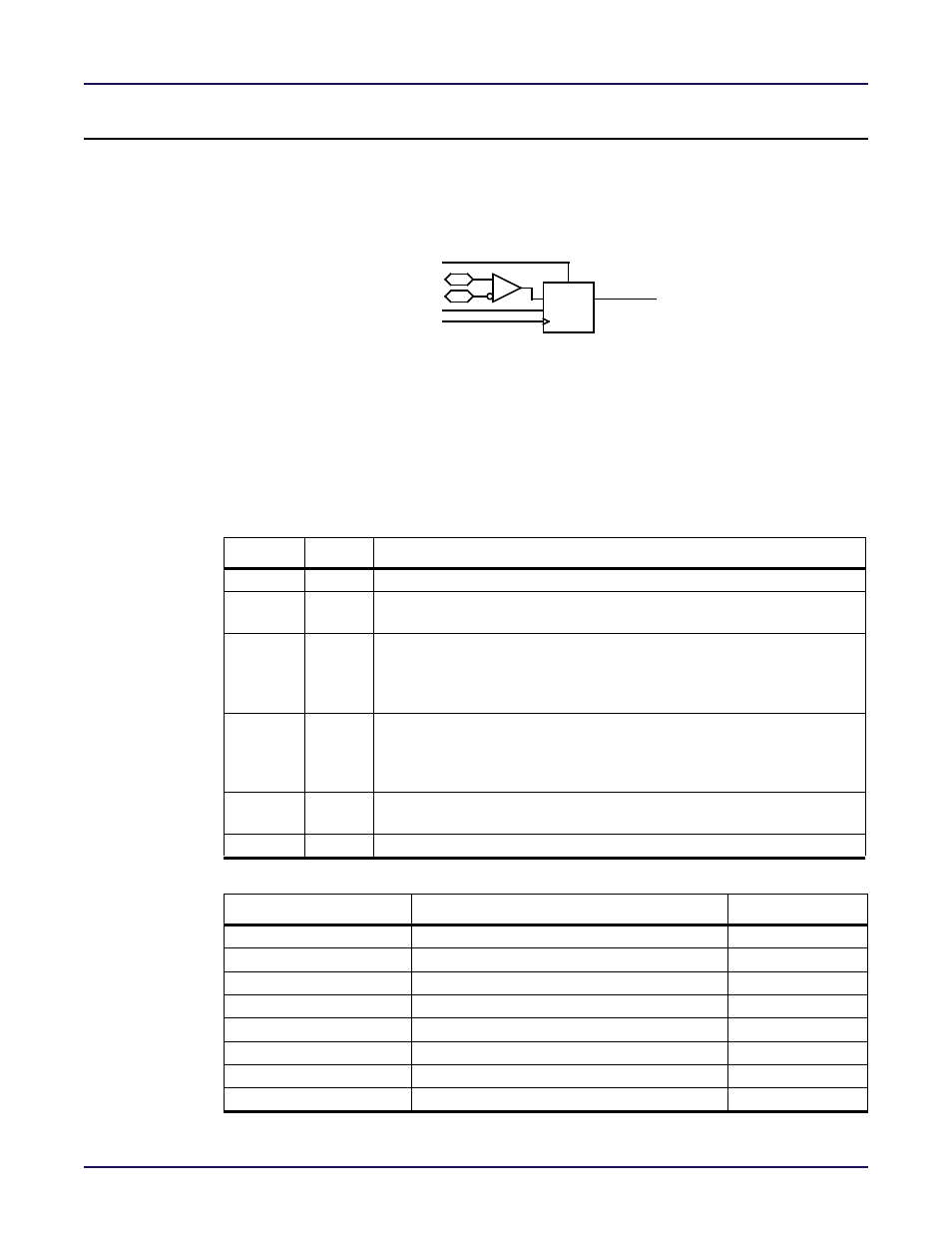

Figure 1-11: IPAD_DIFFD Logic Symbol

IPAD_DIFFD is a registered differential input pad. Driving rstn low performs either a

synchronous or asynchronous reset of the input register as determined by the value of the

rstmode parameter. Upon assertion of the rstn signal, the input register is initialized to the

value determined by the rstvalue parameter.

Table 1-25: Ports

Name

Type

Description

pad

Device pad.

padn

Comlement device pad. The padn input must be driven with the logical

complement of the pad input.

rstn

Reset input. The active-low rstn input performs either a synchronous or

asynchronous set/reset operation as determined by the rstmode parame-

ter. The value that is initialized into the register is determined by the value

of the rstvalue parameter.

data_en

Input Register Clock Enable. A high value on data_en enables the Input

Register to clock the value on pad into the Input Register at the next rising

edge of clk. A low value on data_en allows the Input Register to retain its

current value.

dout

Positive-edge based data output. Data is clocked from the differential

pad to dout on the rising edge of clk.

clk

Clock.

Table 1-26: Parameters

Parameter

Defined Values

Default Value

locationp

locationn

iostandard

“LVDS”

rstmode

rstvalue

pvt_comp

“none”, “own”

“none”

odt

“off”, “on”

“off”

termination

“50”, “60”, “75”, “100”, “120”, “240”

“50”

input

input

input

input

output

input

“

““

“

““

See

“sync”, “async”

“async”

“low”, “high”

“low”